Question: 2 - Consider a dual - core ( P 1 and P 2 ) SMP system with fully - associative caches, write - back, and

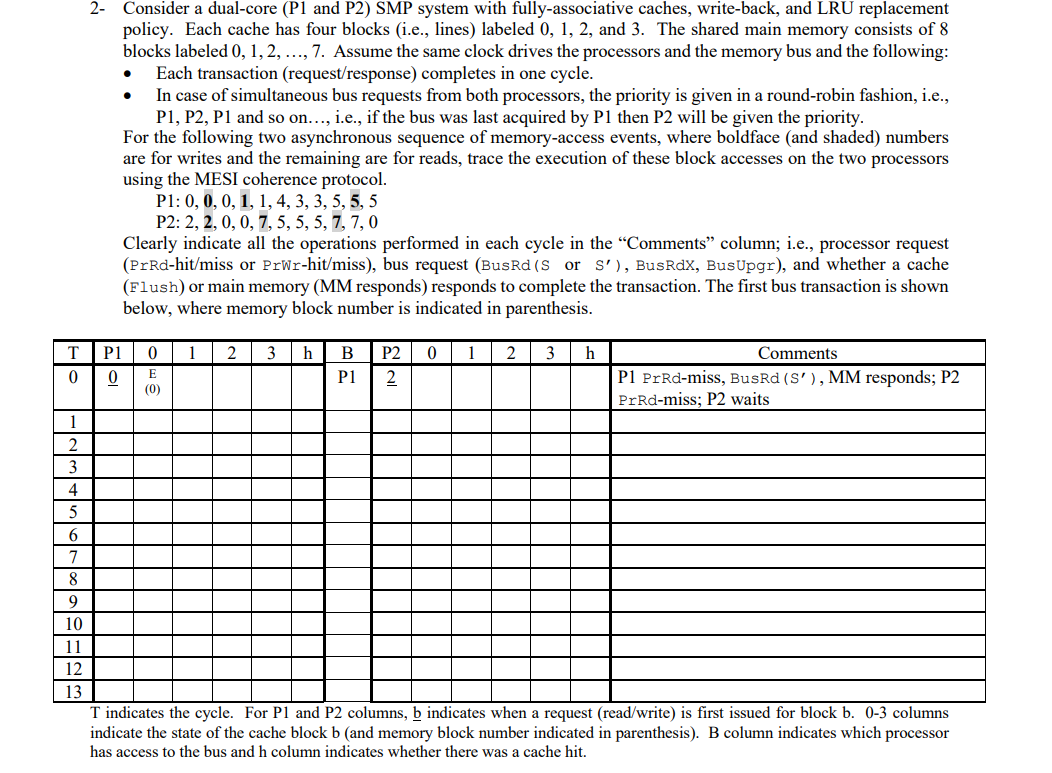

Consider a dualcore P and P SMP system with fullyassociative caches, writeback, and LRU replacement

policy. Each cache has four blocks ie lines labeled and The shared main memory consists of

blocks labeled dots, Assume the same clock drives the processors and the memory bus and the following:

Each transaction requestresponse completes in one cycle.

In case of simultaneous bus requests from both processors, the priority is given in a roundrobin fashion, ie

and so on ie if the bus was last acquired by P then P will be given the priority.

For the following two asynchronous sequence of memoryaccess events, where boldface and shaded numbers

are for writes and the remaining are for reads, trace the execution of these block accesses on the two processors

using the MESI coherence protocol.

P:

P:

Clearly indicate all the operations performed in each cycle in the "Comments" column; ie processor request

PrRdhitmiss or PrWrhitmiss bus request BusRd S or BusRdX, BusUpgr and whether a cache

Flush or main memory MM responds responds to complete the transaction. The first bus transaction is shown

below, where memory block number is indicated in parenthesis.

T indicates the cycle. For P and P columns, indicates when a request readwrite is first issued for block b columns

indicate the state of the cache block and memory block number indicated in parenthesis B column indicates which processor

has access to the bus and column indicates whether there was a cache hit.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock