Question: 2. Consider the following hypothetical CPU LI cache and MMU specification: Cache specification 8-bit CPU (physical and virtual memory addresses have 8 bits and byte-

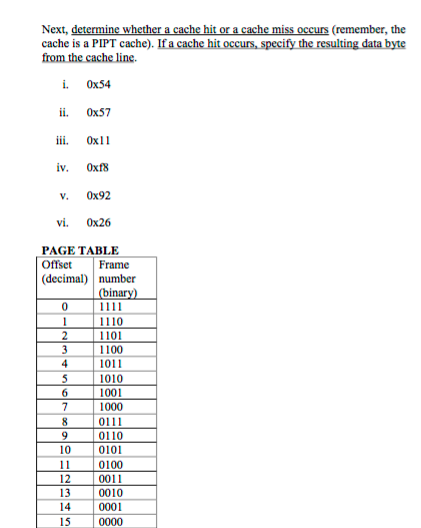

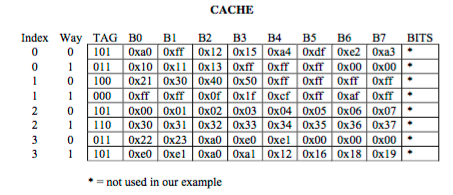

2. Consider the following hypothetical CPU LI cache and MMU specification: Cache specification 8-bit CPU (physical and virtual memory addresses have 8 bits and byte- addressable memory 8-entry total number of cache lines), 2-way set associative LI cache. Cache line size: 8 bytes Cache architecture based on PIPT (physically indexed, physically tagged) MMUspecification 8-bit virtual addresses Single-level paging (i.e., single page table). Page size 16 bytes a. How many bits do we need for the i) tag, ii) cache index, and iii) cache offset? Describe why. b. How many bits do we need for i.) page offset, and ii) page number of the virtual address? c. If you look at the tag bits in the cache below, you will find the same tag bits associated with different cache lines. i. Is it possible for the same tag to be in different cache lines corresponding to different indices? Explain your answer. ii. Is it possible for the same tag to be in different cache lines corresponding to the same index (but a different way? Explain your answer. d. Consider the page table and cache (with contents) below. First, determine given below. 2. Consider the following hypothetical CPU LI cache and MMU specification: Cache specification 8-bit CPU (physical and virtual memory addresses have 8 bits and byte- addressable memory 8-entry total number of cache lines), 2-way set associative LI cache. Cache line size: 8 bytes Cache architecture based on PIPT (physically indexed, physically tagged) MMUspecification 8-bit virtual addresses Single-level paging (i.e., single page table). Page size 16 bytes a. How many bits do we need for the i) tag, ii) cache index, and iii) cache offset? Describe why. b. How many bits do we need for i.) page offset, and ii) page number of the virtual address? c. If you look at the tag bits in the cache below, you will find the same tag bits associated with different cache lines. i. Is it possible for the same tag to be in different cache lines corresponding to different indices? Explain your answer. ii. Is it possible for the same tag to be in different cache lines corresponding to the same index (but a different way? Explain your answer. d. Consider the page table and cache (with contents) below. First, determine given below

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts