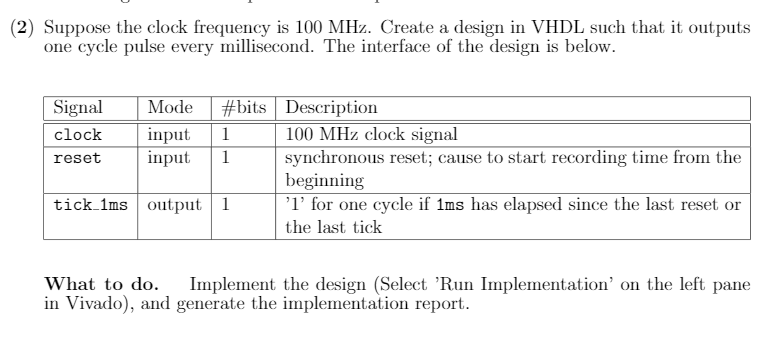

Question: (2) Suppose the clock frequency is 100 MHz. Create a design in VHDL such that it outputs one cycle pulse every millisecond. The interface of

(2) Suppose the clock frequency is 100 MHz. Create a design in VHDL such that it outputs one cycle pulse every millisecond. The interface of the design is below. Signal Mode #bits Description clock input 1 100 MHz clock signal reset input 1 synchronous reset; cause to start recording time from the beginning tick_1ms output 1 'l' for one cycle if 1ms has elapsed since the last reset or the last tick What to do. Implement the design (Select 'Run Implementation on the left pane in Vivado), and generate the implementation report. (2) Suppose the clock frequency is 100 MHz. Create a design in VHDL such that it outputs one cycle pulse every millisecond. The interface of the design is below. Signal Mode #bits Description clock input 1 100 MHz clock signal reset input 1 synchronous reset; cause to start recording time from the beginning tick_1ms output 1 'l' for one cycle if 1ms has elapsed since the last reset or the last tick What to do. Implement the design (Select 'Run Implementation on the left pane in Vivado), and generate the implementation report

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts