Question: 2) Write a VHDL code for an AND gate. 3) Add your * vhd by Add Sources, Add or create design sources to your project.

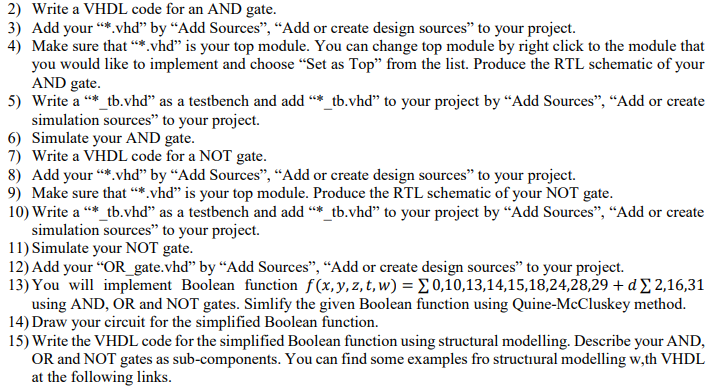

2) Write a VHDL code for an AND gate. 3) Add your "* vhd by "Add Sources, Add or create design sources to your project. 4) Make sure that "* vhd is your top module. You can change top module by right click to the module that you would like to implement and choose "Set as Top from the list. Produce the RTL schematic of your AND gate. 5) Write a "*_tb.vhd as a testbench and add "*_tb.vhd to your project by Add Sources, Add or create simulation sources" to your project. 6) Simulate your AND gate. 7) Write a VHDL code for a NOT gate. 8) Add your "* vhd by Add Sources, Add or create design sources to your project. 9) Make sure that "* vhd is your top module. Produce the RTL schematic of your NOT gate. 10) Write a *_tb.vhd" as a testbench and add "*_tb.vhd" to your project by Add Sources, Add or create simulation sources to your project. 11) Simulate your NOT gate. 12) Add your OR_gate.vhd by Add Sources, Add or create design sources to your project. 13) You will implement Boolean function f(x,y,z,t, w) = 0,10,13,14,15,18,24,28,29 + d 2,16,31 using AND, OR and NOT gates. Simlify the given Boolean function using Quine-McCluskey method. 14) Draw your circuit for the simplified Boolean function. 15) Write the VHDL code for the simplified Boolean function using structural modelling. Describe your AND, OR and NOT gates as sub-components. You can find some examples fro structural modelling w,th VHDL at the following links. 2) Write a VHDL code for an AND gate. 3) Add your "* vhd by "Add Sources, Add or create design sources to your project. 4) Make sure that "* vhd is your top module. You can change top module by right click to the module that you would like to implement and choose "Set as Top from the list. Produce the RTL schematic of your AND gate. 5) Write a "*_tb.vhd as a testbench and add "*_tb.vhd to your project by Add Sources, Add or create simulation sources" to your project. 6) Simulate your AND gate. 7) Write a VHDL code for a NOT gate. 8) Add your "* vhd by Add Sources, Add or create design sources to your project. 9) Make sure that "* vhd is your top module. Produce the RTL schematic of your NOT gate. 10) Write a *_tb.vhd" as a testbench and add "*_tb.vhd" to your project by Add Sources, Add or create simulation sources to your project. 11) Simulate your NOT gate. 12) Add your OR_gate.vhd by Add Sources, Add or create design sources to your project. 13) You will implement Boolean function f(x,y,z,t, w) = 0,10,13,14,15,18,24,28,29 + d 2,16,31 using AND, OR and NOT gates. Simlify the given Boolean function using Quine-McCluskey method. 14) Draw your circuit for the simplified Boolean function. 15) Write the VHDL code for the simplified Boolean function using structural modelling. Describe your AND, OR and NOT gates as sub-components. You can find some examples fro structural modelling w,th VHDL at the following links

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts