Question: 3. Consider the following DLX code. Assume that initial values of all registers and memory are zero a) In this part assume there is no

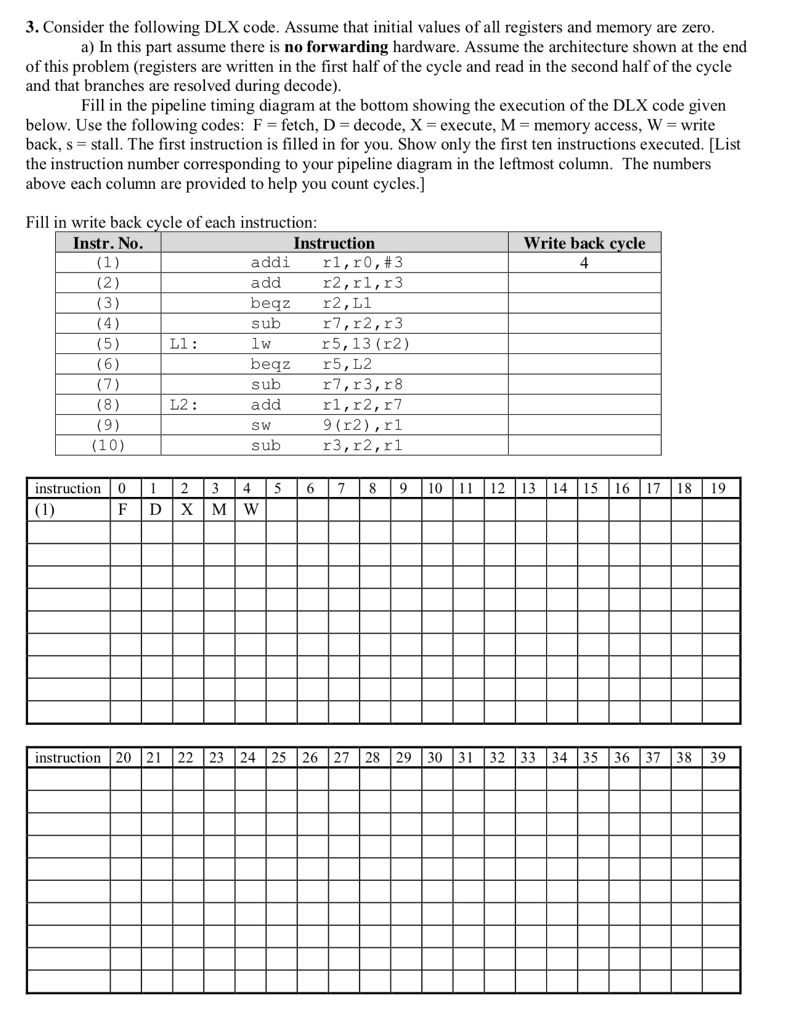

3. Consider the following DLX code. Assume that initial values of all registers and memory are zero a) In this part assume there is no forwarding hardware. Assume the architecture shown at the end of this problem (registers are written in the first half of the cycle and read in the second half of the cycle and that branches are resolved during decode) Fill in the pipeline timing diagram at the bottom showing the execution of the DLX code given below. Use the following codes: F = fetch, D-decode, X-execute, M-memory access, W-write back, s -stall. The first instruction is filled in for you. Show only the first ten instructions executed. [List the instruction number corresponding to your pipeline diagram in the leftmost column. The numbers above each column are provided to help you count cycles.] Fill in write back cycle of each instruction: Instr. No Instruction Write back cycle 4 addi r1,r0,#3 add begzr2,L1 sub r2,rl,r3 r7,r2,r3 r5,13 (r2) LI : begzr5,L2 sub add SW sub r7,r3,r8 rl,r2,r7 9 (r2),rl r3,r2,r1 L2: (10) nstruction instruction 20 21 22 23 2425 26 2728 29 3031 32 33 34 35 36 37 38 39

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts