Question: 3. For this problem, assume a two-level cache. L1 cache is split-i.e. separate instruction and data caches-while the L2 cache is unified. The per access

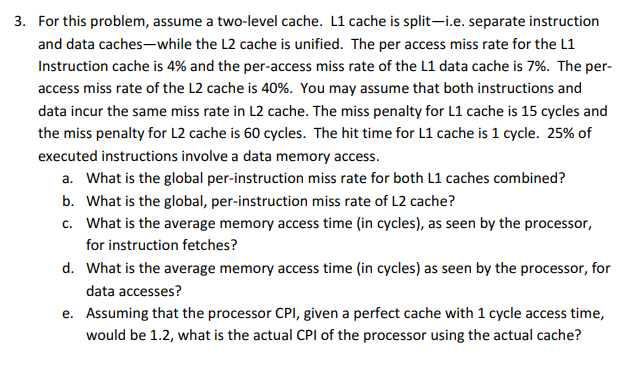

3. For this problem, assume a two-level cache. L1 cache is split-i.e. separate instruction and data caches-while the L2 cache is unified. The per access miss rate for the L1 Instruction cache is 4% and the per-access miss rate of the L1 data cache is 7%. The per access miss rate of the L2 cache is 40%. You may assume that both instructions and data incur the same miss rate in L2 cache. The miss penalty for L1 cache is 15 cycles and the miss penalty for L2 cache is 60 cycles. The hit time for L1 cache is 1 cycle. 25% of executed instructions involve a data memory access What is the global per-instruction miss rate for both L1 caches combined? What is the global, per-instruction miss rate of L2 cache? What is the average memory access time (in cycles), as seen by the processor, for instruction fetches? What is the average memory access time (in cycles) as seen by the processor, for data accesses? Assuming that the processor CPI, given a perfect cache with 1 cycle access time, would be 1.2, what is the actual CPl of the processor using the actual cache? a. b. c. d. e. 3. For this problem, assume a two-level cache. L1 cache is split-i.e. separate instruction and data caches-while the L2 cache is unified. The per access miss rate for the L1 Instruction cache is 4% and the per-access miss rate of the L1 data cache is 7%. The per access miss rate of the L2 cache is 40%. You may assume that both instructions and data incur the same miss rate in L2 cache. The miss penalty for L1 cache is 15 cycles and the miss penalty for L2 cache is 60 cycles. The hit time for L1 cache is 1 cycle. 25% of executed instructions involve a data memory access What is the global per-instruction miss rate for both L1 caches combined? What is the global, per-instruction miss rate of L2 cache? What is the average memory access time (in cycles), as seen by the processor, for instruction fetches? What is the average memory access time (in cycles) as seen by the processor, for data accesses? Assuming that the processor CPI, given a perfect cache with 1 cycle access time, would be 1.2, what is the actual CPl of the processor using the actual cache? a. b. c. d. e

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts