Question: 31. In a single-cycle processor diagrammed in Fig. 2, which two of add, beq, Id, sd enable Regw rite? (31A). add, beq (31B). add, ld

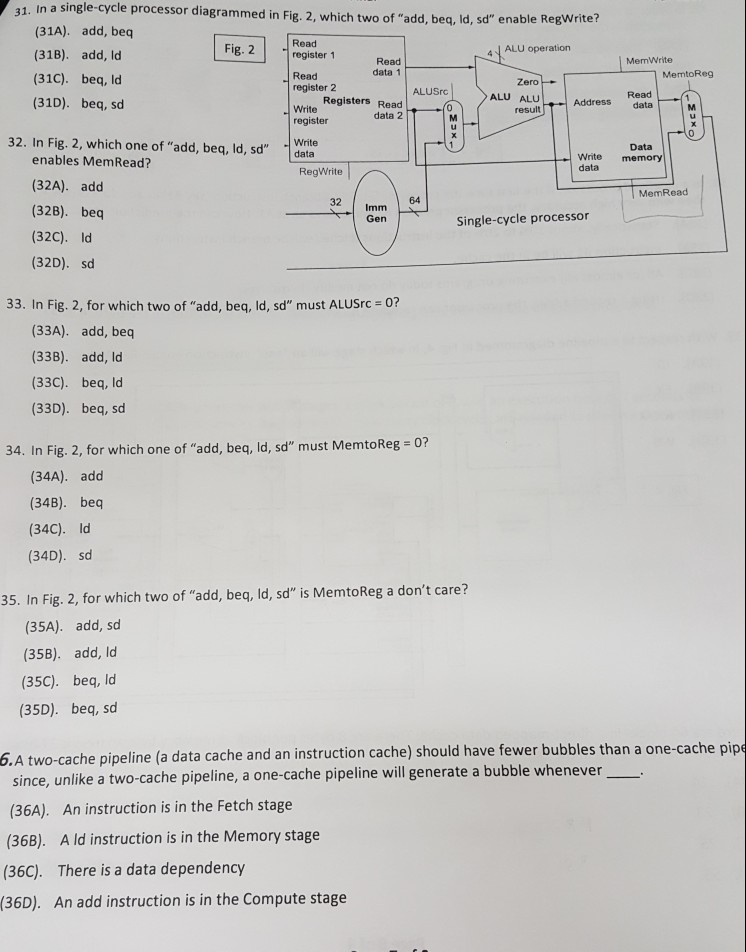

31. In a single-cycle processor diagrammed in Fig. 2, which two of "add, beq, Id, sd" enable Regw rite? (31A). add, beq (31B). add, ld (31C). beq, ld (31D). beq, sd Read register 1 Read register 2 Write register Write Fig. 2 ALU operation Read data 1 MemtoReg Zero ReadM ALUSrc ALU AL Address data Registers Read data 2 Lu 32. In Fig. 2, which one of "add, beq, ld, sd" Data data Write memory data enables MemRead? (32A). add (32B). beq (32C). ld (32D). sd RegWrite MemRead 32 64 Imm Gen Single-cycle processor 33. In Fig. 2, for which two of "add, beq, ld, sd" must ALUSrc 0? (33A). add, beq (33B). add, ld (33C). beq, ld (33D). beq, sd 34. In Fig. 2, for which one of "add, beq, Id, sd" must MemtoReg 0? (34A). add (34B). beq (34C). ld (34D). sd 35. In Fig. 2, for which two of "add, beq, Id, sd" is MemtoReg a don't care? (35A). add, sd (35B). add, ld (35C). beq, ld (35D). beq, sd two-cache pipeline (a data cache and an instruction cache) should have fewer bubbles than a one-cache pip since, unlike a two-cache pipeline, a one-cache pipeline will generate a bubble whenever- (36A). An instruction is in the Fetch stage (36B). A ld instruction is in the Memory stage (36C). There is a data dependency 6.A (36D). An add instruction is in the Compute stage

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts