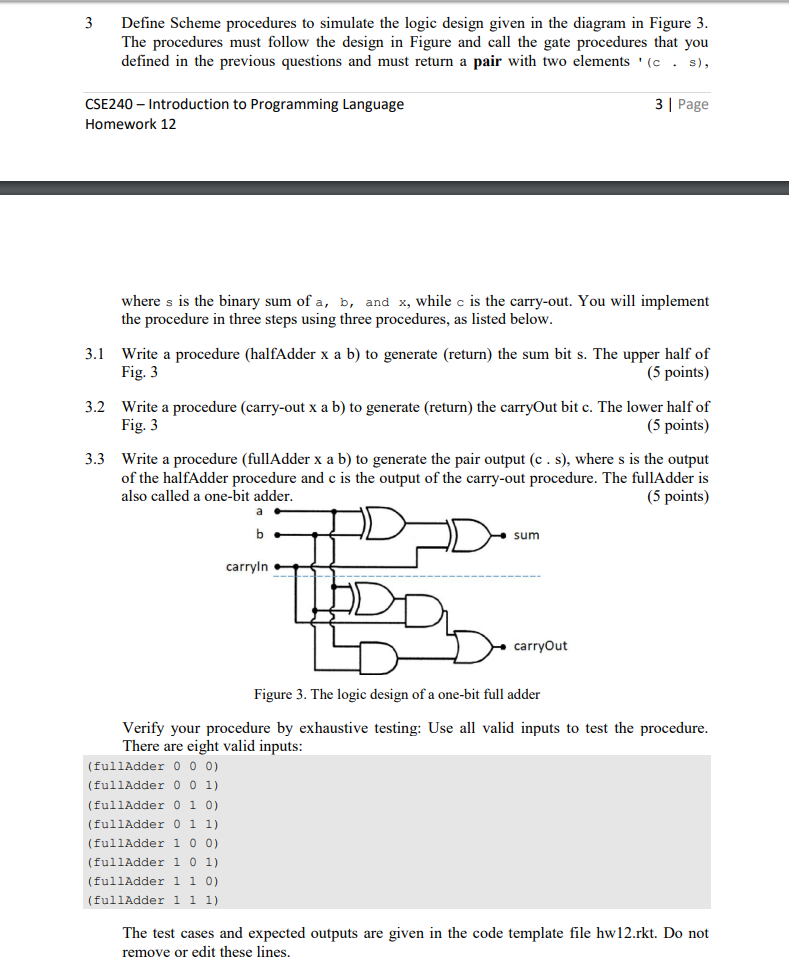

Question: 3Define Scheme procedures to simulate the logic design given in the diagram in Figure 3 The procedures must follow the design in Figure and call

3Define Scheme procedures to simulate the logic design given in the diagram in Figure 3 The procedures must follow the design in Figure and call the gate procedures that you defined in the previous questions and must return a pair with two elements '(cs 3 | Page CSE240 Introduction to Programming Language Homework 12 where s is the binary sum of a, b, and x, while c is the carry-out. You will implement the procedure in three steps using three procedures, as listed below 3.1 Write a procedure (halfAdder x a b) to generate (return) the sum bit s. The upper half of Fig. 3 (5 points) 3.2 Write a procedure (carry-out x a b) to generate (return) the carryOut bit c. The lower half of Fig. 3 (5 points) 3.3 Write a procedure (fullAdder x a b) to generate the pair output (c. s), where s is the output of the halfAdder procedure and c is the output of the carry-out procedure. The fullAdder is also called a one-bit adder (5 points) sum carryln carryOut Figure 3. The logic design of a one-bit full adder Verify your procedure by exhaustive testing: Use all valid inputs to test the procedure There are eight valid inputs (fullAdder 0 0 0) (fullAdder 0 0 1) (fullAdder 0 1 0) (fullAdder 0 1 1) (fullAdder 1 0 0) (fullAdder 1 0 1) (fullAdder 1 1 0) (fullAdder 1 1 1) The test cases and expected outputs are given in the code template file hw12.rkt. Do not remove or edit these lines. 3Define Scheme procedures to simulate the logic design given in the diagram in Figure 3 The procedures must follow the design in Figure and call the gate procedures that you defined in the previous questions and must return a pair with two elements '(cs 3 | Page CSE240 Introduction to Programming Language Homework 12 where s is the binary sum of a, b, and x, while c is the carry-out. You will implement the procedure in three steps using three procedures, as listed below 3.1 Write a procedure (halfAdder x a b) to generate (return) the sum bit s. The upper half of Fig. 3 (5 points) 3.2 Write a procedure (carry-out x a b) to generate (return) the carryOut bit c. The lower half of Fig. 3 (5 points) 3.3 Write a procedure (fullAdder x a b) to generate the pair output (c. s), where s is the output of the halfAdder procedure and c is the output of the carry-out procedure. The fullAdder is also called a one-bit adder (5 points) sum carryln carryOut Figure 3. The logic design of a one-bit full adder Verify your procedure by exhaustive testing: Use all valid inputs to test the procedure There are eight valid inputs (fullAdder 0 0 0) (fullAdder 0 0 1) (fullAdder 0 1 0) (fullAdder 0 1 1) (fullAdder 1 0 0) (fullAdder 1 0 1) (fullAdder 1 1 0) (fullAdder 1 1 1) The test cases and expected outputs are given in the code template file hw12.rkt. Do not remove or edit these lines

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts