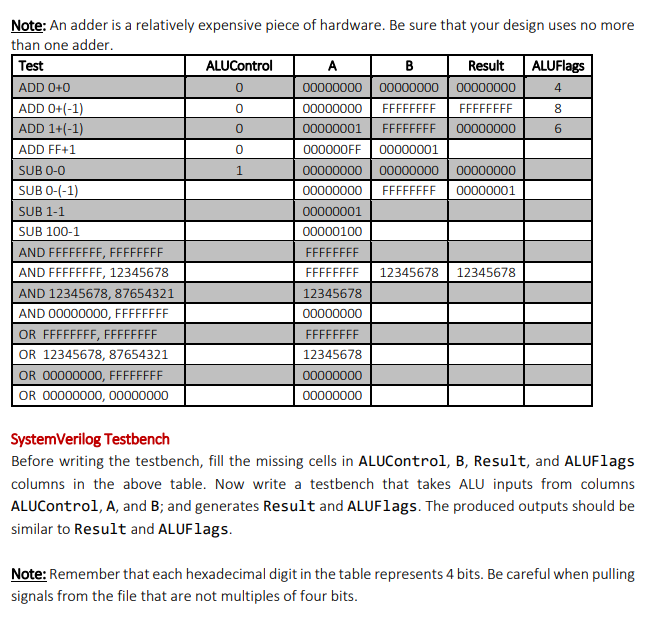

Question: 4 1 Note: An adder is a relatively expensive piece of hardware. Be sure that your design uses no more than one adder. Test ALUControl

4 1 Note: An adder is a relatively expensive piece of hardware. Be sure that your design uses no more than one adder. Test ALUControl . B Result ALUFlags ADD 0+0 0 000000000000000000000000 ADD O+(-1) 0 00000000 FFFFFFFF FFFFFFFF 8 ADD 1+(-1) 0 00000001 | FFFFFFFF 00000000 6 ADD FF+1 0 000000FF 00000001 SUB 0-0 000000000000000000000000 SUB O-(-1) 00000000FFFFFFFF 00000001 SUB 1-1 00000001 SUB 100-1 00000100 AND FFFFFFFF, FFFFFFFF FFFFFFFF AND FFFFFFFF, 12345678 FFFFFFFF 12345678 12345678 AND 12345678, 87654321 12345678 AND 00000000, FFFFFFFF 00000000 OR FFFFFFFF, FFFFFFFF FFFFFFFF OR 12345678, 87654321 12345678 OR 00000000, FFFFFFFF 00000000 OR 00000000, 00000000 00000000 SystemVerilog Testbench Before writing the testbench, fill the missing cells in ALUControl, B, Result, and ALUFlags columns in the above table. Now write a testbench that takes ALU inputs from columns ALUControl, A, and B; and generates Result and ALUFlags. The produced outputs should be similar to Result and ALUFlags. Note: Remember that each hexadecimal digit in the table represents 4 bits. Be careful when pulling signals from the file that are not multiples of four bits. 4 1 Note: An adder is a relatively expensive piece of hardware. Be sure that your design uses no more than one adder. Test ALUControl . B Result ALUFlags ADD 0+0 0 000000000000000000000000 ADD O+(-1) 0 00000000 FFFFFFFF FFFFFFFF 8 ADD 1+(-1) 0 00000001 | FFFFFFFF 00000000 6 ADD FF+1 0 000000FF 00000001 SUB 0-0 000000000000000000000000 SUB O-(-1) 00000000FFFFFFFF 00000001 SUB 1-1 00000001 SUB 100-1 00000100 AND FFFFFFFF, FFFFFFFF FFFFFFFF AND FFFFFFFF, 12345678 FFFFFFFF 12345678 12345678 AND 12345678, 87654321 12345678 AND 00000000, FFFFFFFF 00000000 OR FFFFFFFF, FFFFFFFF FFFFFFFF OR 12345678, 87654321 12345678 OR 00000000, FFFFFFFF 00000000 OR 00000000, 00000000 00000000 SystemVerilog Testbench Before writing the testbench, fill the missing cells in ALUControl, B, Result, and ALUFlags columns in the above table. Now write a testbench that takes ALU inputs from columns ALUControl, A, and B; and generates Result and ALUFlags. The produced outputs should be similar to Result and ALUFlags. Note: Remember that each hexadecimal digit in the table represents 4 bits. Be careful when pulling signals from the file that are not multiples of four bits

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts