Question: 4.3.a-Write a 2-level expression using XOR () and NOR for the compare function fcomp which compares two 8 bits numbers Al7:0] Xt7-0and BI7:0]teHand evaluates to

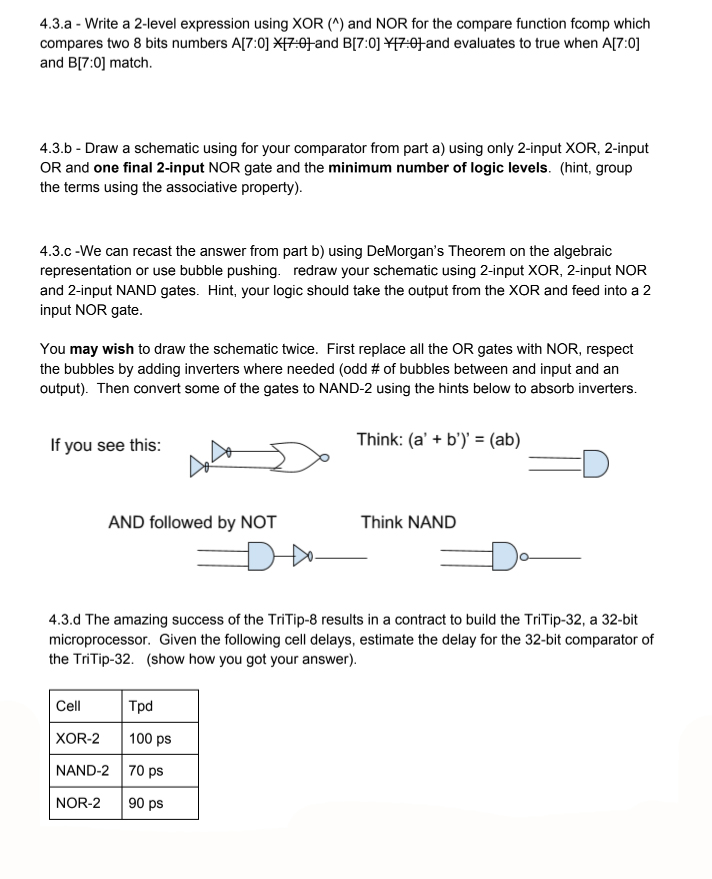

4.3.a-Write a 2-level expression using XOR () and NOR for the compare function fcomp which compares two 8 bits numbers Al7:0] Xt7-0and BI7:0]teHand evaluates to true when A[7:0] and BI7:0] match 4.3.b - Draw a schematic using for your comparator from part a) using only 2-input XOR, 2-input OR and one final 2-input NOR gate and the minimum number of logic levels. (hint, group the terms using the associative property) 4.3.c-We can recast the answer from part b) using DeMorgan's Theorem on the algebraic representation or use bubble pushing. redraw your schematic using 2-input XOR, 2-input NOR and 2-input NAND gates. Hint, your logic should take the output from the XOR and feed into a 2 input NOR gate. You may wish to draw the schematic twice. First replace all the OR gates with NOR, respect the bubbles by adding inverters where needed (odd # of bubbles between and input and an output). Then convert some of the gates to NAND-2 using the hints below to absorb inverters. If you see this Think: (a+ b') - (ab) AND followed by NOT Think NAND 4.3.d The amazing success of the TriTip-8 results in a contract to build the TriTip-32, a 32-bit microprocessor. Given the following cell delays, estimate the delay for the 32-bit comparator of the TriTip-32. (show how you got your answer). Cell Tpd XOR-2100 ps NAND-2 70 ps NOR-2 90 ps 4.3.a-Write a 2-level expression using XOR () and NOR for the compare function fcomp which compares two 8 bits numbers Al7:0] Xt7-0and BI7:0]teHand evaluates to true when A[7:0] and BI7:0] match 4.3.b - Draw a schematic using for your comparator from part a) using only 2-input XOR, 2-input OR and one final 2-input NOR gate and the minimum number of logic levels. (hint, group the terms using the associative property) 4.3.c-We can recast the answer from part b) using DeMorgan's Theorem on the algebraic representation or use bubble pushing. redraw your schematic using 2-input XOR, 2-input NOR and 2-input NAND gates. Hint, your logic should take the output from the XOR and feed into a 2 input NOR gate. You may wish to draw the schematic twice. First replace all the OR gates with NOR, respect the bubbles by adding inverters where needed (odd # of bubbles between and input and an output). Then convert some of the gates to NAND-2 using the hints below to absorb inverters. If you see this Think: (a+ b') - (ab) AND followed by NOT Think NAND 4.3.d The amazing success of the TriTip-8 results in a contract to build the TriTip-32, a 32-bit microprocessor. Given the following cell delays, estimate the delay for the 32-bit comparator of the TriTip-32. (show how you got your answer). Cell Tpd XOR-2100 ps NAND-2 70 ps NOR-2 90 ps

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts