Question: 5. (10 points) Consider the following instruction sequence executing on the 5-stage MIPS pipelined processor. lw $1,8($2) add $3, $2, $4 SW $1, 16($3) sub

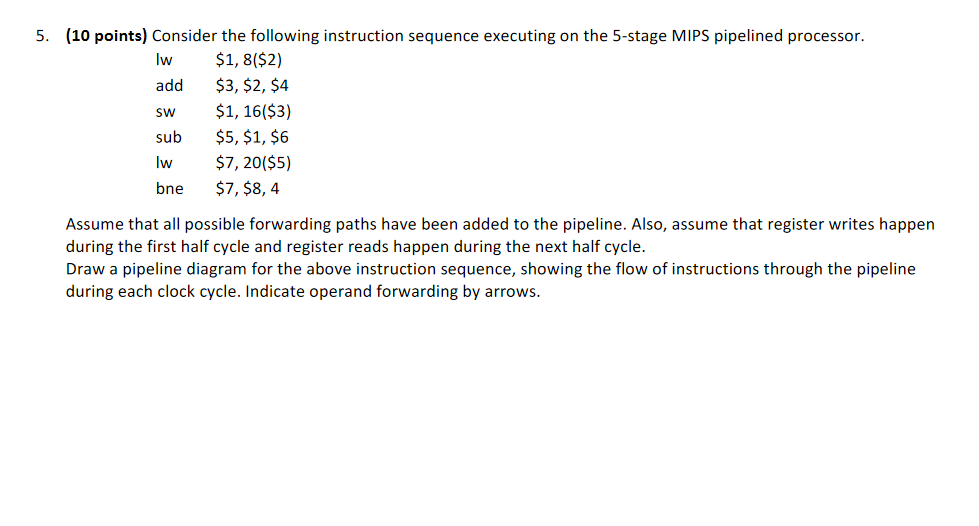

5. (10 points) Consider the following instruction sequence executing on the 5-stage MIPS pipelined processor. lw $1,8($2) add $3, $2, $4 SW $1, 16($3) sub $5, $1, $6 lw $7, 20($5) bne $7, $8,4 Assume that all possible forwarding paths have been added to the pipeline. Also, assume that register writes happen during the first half cycle and register reads happen during the next half cycle. Draw a pipeline diagram for the above instruction sequence, showing the flow of instructions through the pipeline during each clock cycle. Indicate operand forwarding by arrows

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts