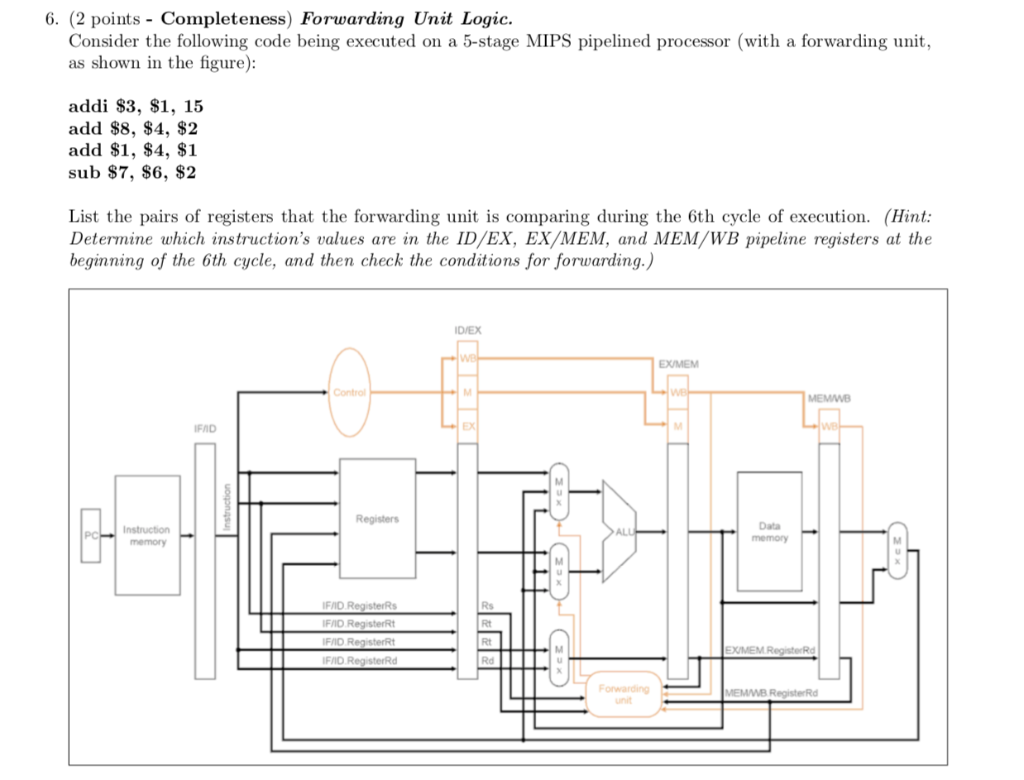

Question: 6. (2 points Completeness) Forwarding Unit Logic. Consider the following code being executed on a 5-stage MIPS pipelined processor (with a forwarding unit, as shown

6. (2 points Completeness) Forwarding Unit Logic. Consider the following code being executed on a 5-stage MIPS pipelined processor (with a forwarding unit, as shown in the figure): addi $3, $1, 15 add $8, $4, $2 add $1, $4, $1 sub $7, $6, $2 List the pairs of registers that the forwarding unit is comparing during the 6th cycle of execution. (Hint: Determine which instruction's values are in the ID/EX, EX/MEM, and MEM/WB pipeline registers at the beginning of the 6th cycle, and then check the conditions for forwarding.) IDIEX FAD Ex Data FAD Registe Rt egisterRt Rt orwarding unit 5. (2 points - Completeness) Branch delay slot Consider the following piece of code. To enable greater performance, the compiler should determine what instruction could be safely moved into the branch delay slot (replacing the nop). What choices does the compiler have? Mention all instructions that could be moved into the BDS. (Assume that software register renaming is disabled. Also, instruction re-ordering optimizations are disabled.) lw $4, 4($1) subi $5, $2, 8 add S3, S4, $1 beq S4, 85, label nop sub $6, $3, $2 add $3, $5, $1 ori $5, $6, 2 label: and S2, $4, $1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts