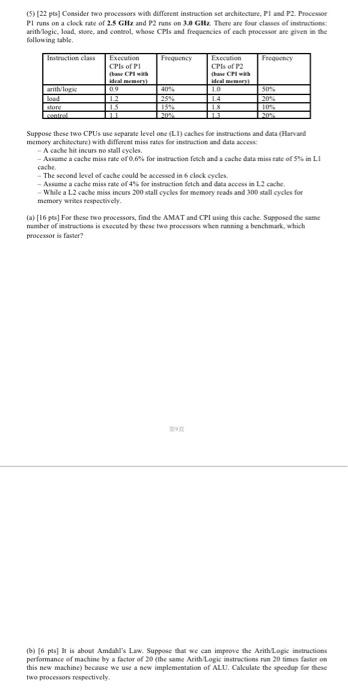

Question: (5) 22 pos Consider two processors with different instruction set architecture, Plund P2. Procesor Pl runs on a clock rate of 2.5 GHz and 2

(5) 22 pos Consider two processors with different instruction set architecture, Plund P2. Procesor Pl runs on a clock rate of 2.5 GHz and 2 runs on Git. There are four classes of instructions anilogic load, Store, and control, whose Pls and frequencies of each processere pivnih following table Instructie class Frequency Frequency Execution CPs of PI Ch desde 09 Execution CPs of 12 CH wear 10 athlon load san 40 294 ESP 2003 LAD Suppose these two CPUs se separate level on Ll) caches fie instructions and data (Harvard memory architecture) with different mis rates for intruction and data A cache hit incurs no stall cycles. Assume a cache miss rate or 0,6% for instruction Catch and a cache data istute of Sin LI cache The second level of cache could be accessed in clockeydes Arcome a cache mie rate of t' for instruction falch and data access in 2 cache While a L2 cache miss incurs 200 stall cycles for memory ads and 300 stall cycles for memcy writes respectively 16 pe Fathese two processors, find the AMAT and CPt using this cache. Supposed the same number of instruction is executed by these two procession when running a benchmark, which process is ater? 10) [6 pts is about Amir's Law. Suppose that we can improve the Arith Logie intructions performance of machine by a factor of 20 (the same Arith Logic instructions rum 20 times fasterom this new machine) because we us a new implementation of ALU. Calculate the speed up for these To proceso pectively

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts