Question: 5. Using the basic, generic 2K x 8 memory device below that has tristate outputs controlled by an output enable, oe, signal, use 4 of

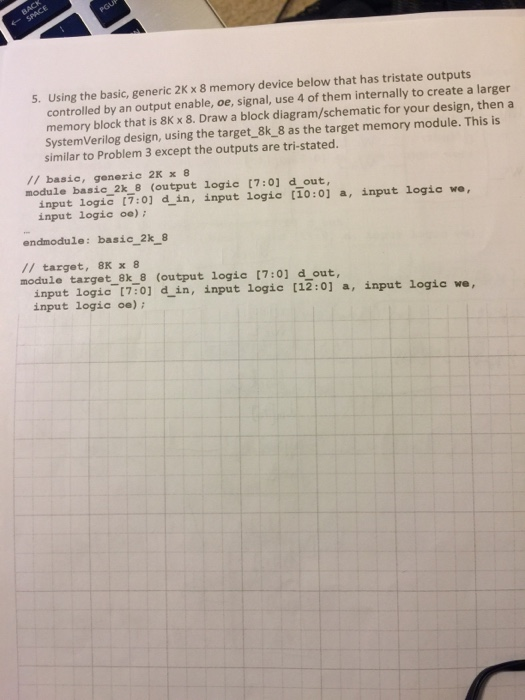

5. Using the basic, generic 2K x 8 memory device below that has tristate outputs controlled by an output enable, oe, signal, use 4 of them internally to create a larger memory block that is 8K x 8. Draw a block diagram/schematic for your design, then a SystemVerilog design, using the target_8k 8 as the target memory module. This is similar to Problem 3 except the outputs are tri-stated. // basic, generic 2K x 8 module basic_2k 8 (output logie [7:0] d out, input logic [7:0j d in, input logic [10:0] a, input logic we, input logic oo) endmodule: basic 2k 8 // target, 8K x 8 module target_8k_8 (output logie [7:01 d out, input logic [7:0] d in, input logic [12:0] a, input logic we, input logic oe)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts