Question: 6 - ) ( 2 0 points ) You've joined a hot new internet startup to build wrist watches with a built - in pager

points You've joined a hot new internet startup to build wrist watches with a builtin pager and

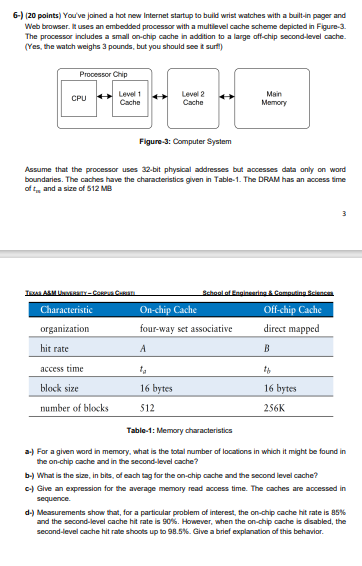

Web browser. It uses an embedded processor with a multilevel cache scheme depicted in Figure

The processor includes a small onchip cache in addition to a large offchip secondlevel cache.

Yes the watch weighs pounds, but you should see it surft

Assume that the processor uses bit physical addresses but accesses data only on word

boundaries. The caches have the characteristics given in Table The DRAM has an access time

of and a size of

Table: Memory characteristics

a For a given word in memory, what is the total number of locations in which it might be found in

the onchip cache and in the secondlevel cache?

b What is the size, in bits, of each tag for the onchip cache and the second level cache?

c Give an expression for the average memory read access time. The caches are apcessed in

sequence.

d Measurements show that, for a particular problem of interest, the onchip cache hit rate is

and the secondlevel cache hit rate is However, when the onchip cache is disabled, the

secondlevel cache hit rate shoots up to Give a brief explanation of this behavior.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock