Question: 8. (10%) Performance Consider two different implementations of the RISC-V instruction set architecture. P1 has a clock rate of 3.0 GHz and CPIs of 1,

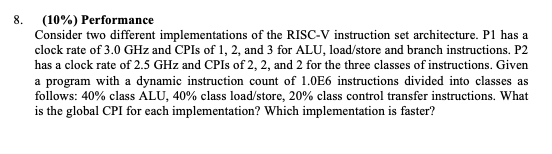

8. (10%) Performance Consider two different implementations of the RISC-V instruction set architecture. P1 has a clock rate of 3.0 GHz and CPIs of 1, 2, and 3 for ALU, load/store and branch instructions. P2 has a clock rate of 2.5 GHz and CPIs of 2, 2, and 2 for the three classes of instructions. Given a program with a dynamic instruction count of 1.0E6 instructions divided into classes as follows: 40% class ALU, 40% class load/store, 20% class control transfer instructions. What is the global CPI for each implementation? Which implementation is faster

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts