Question: 8. Given a DRAM memory chip that is 1M x 1 that is organized into 1024 rows and may be refreshed one row at a

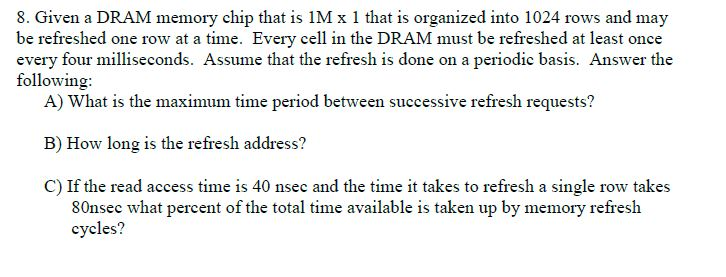

8. Given a DRAM memory chip that is 1M x 1 that is organized into 1024 rows and may be refreshed one row at a time. Every cell in the DRAM must be refreshed at least once every four milliseconds. Assume that the refresh is done on a periodic basis. Answer the following: A) What is the maximum time period between successive refresh requests? B) How long is the refresh address? C) If the read access time is 40 nsec and the time it takes to refresh a single row takes 80nsec what percent of the total time available is taken up by memory refresh cycles? 8. Given a DRAM memory chip that is 1M x 1 that is organized into 1024 rows and may be refreshed one row at a time. Every cell in the DRAM must be refreshed at least once every four milliseconds. Assume that the refresh is done on a periodic basis. Answer the following: A) What is the maximum time period between successive refresh requests? B) How long is the refresh address? C) If the read access time is 40 nsec and the time it takes to refresh a single row takes 80nsec what percent of the total time available is taken up by memory refresh cycles

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts