Question: A 2-bit comparator compares two 2-bit words, A and B, and assets outputs indicating whether the decimal equivalent of word A is less than, greater

A 2-bit comparator compares two 2-bit words, A and B, and assets outputs indicating whether the decimal equivalent of word A is less than, greater than or equal to that of word B. K-map method can be used to derive the minimized equations to describe the behavior of the comparator and Verilog module can be written to test the working of the comparator. Complete the following:

A) Derive minimized equations for the comparator outputs - A less than B, A equal to B, and A greater than B. Done

B) Draw logic diagram. Done

C) Write and test the Verilog Module for this comparator ( this is where I am having issues)

What I have but not passing the complier

module comparator_2bit (a, b, greater, equal, lower);

output greater; output equal; output lower;

input [1:0]a; input [1:0]b;

assign greater = (a>b) ? 1:0; assign equal = (a==b) ? 1:0; assign lower = (a

end module

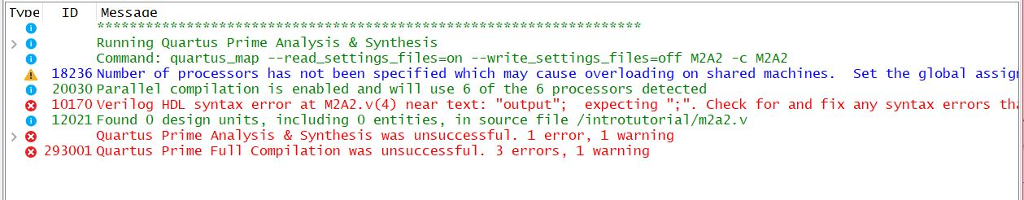

TvDe ID Messaae t e tee te Running Quartus Prime Analysis & Synthesis 0 Command: quartus map --read settings files-on -write settings files-off M2A2 -c M2A2 18236 Number of processors has not been specified which may cause overloading on shared machines. Set the global assig o 20030 Parallel compilation is enabled and wil1 use 6 of the 6 processors detected 3 10170 Verilog HDL syntax error at M2A2. v(4) near text: "output" expecting "". Check for and fix any syntax errors th o 12021 Found 0 design units, including 0 entities, in source file/introtutorial/m2a2.v Quartus Prime Analysis & Synthesis was unsuccessful. 1 error, 1 warning 293001 Quartus Prime Full Compilation was unsuccessful. 3 errors, 1 warning

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts