Question: A 64-bit microprocessor is using a 48-bit system bus and the microprocessor is driven by a 1GHz input clock. The microprocessor is attached to the

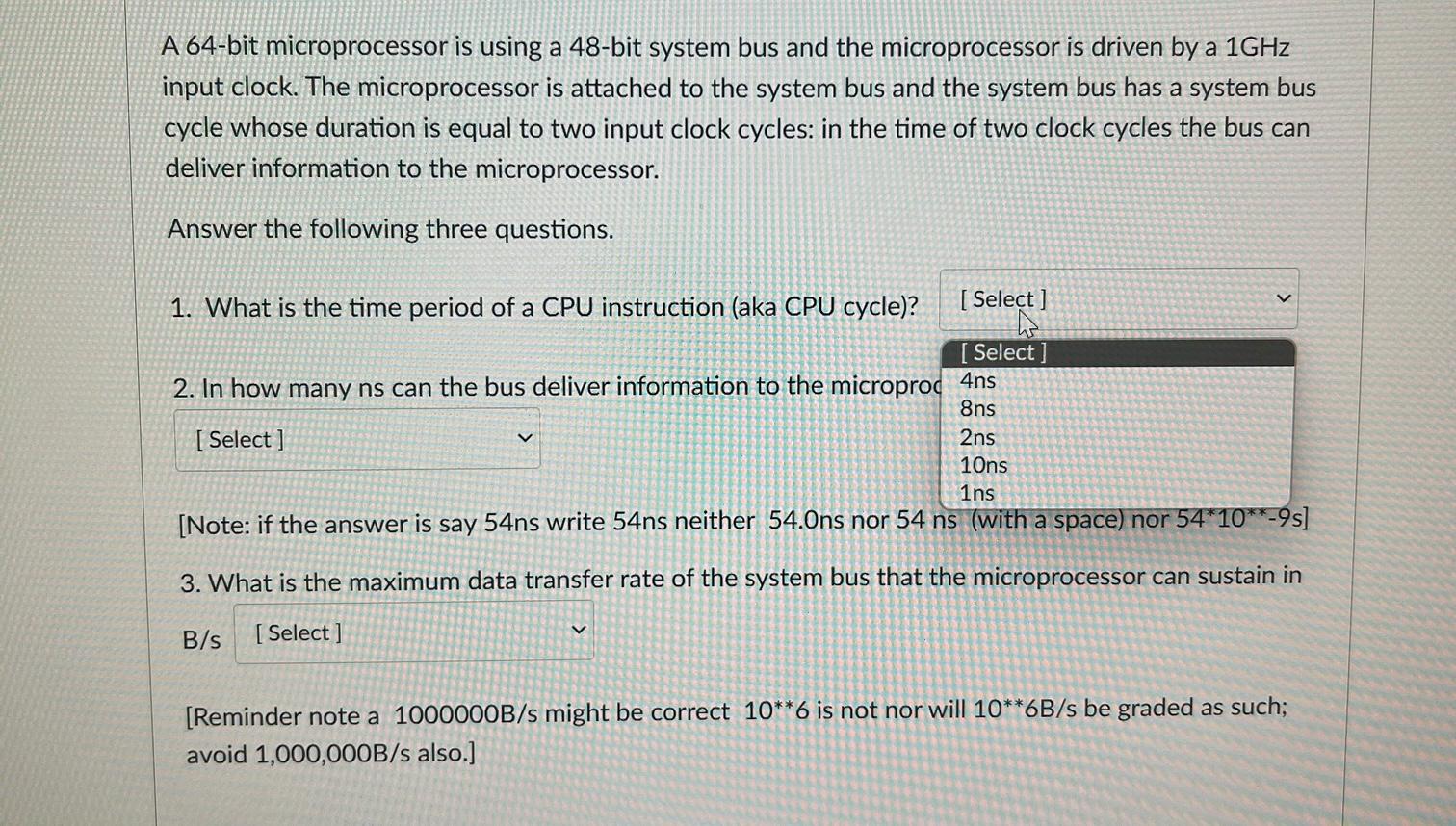

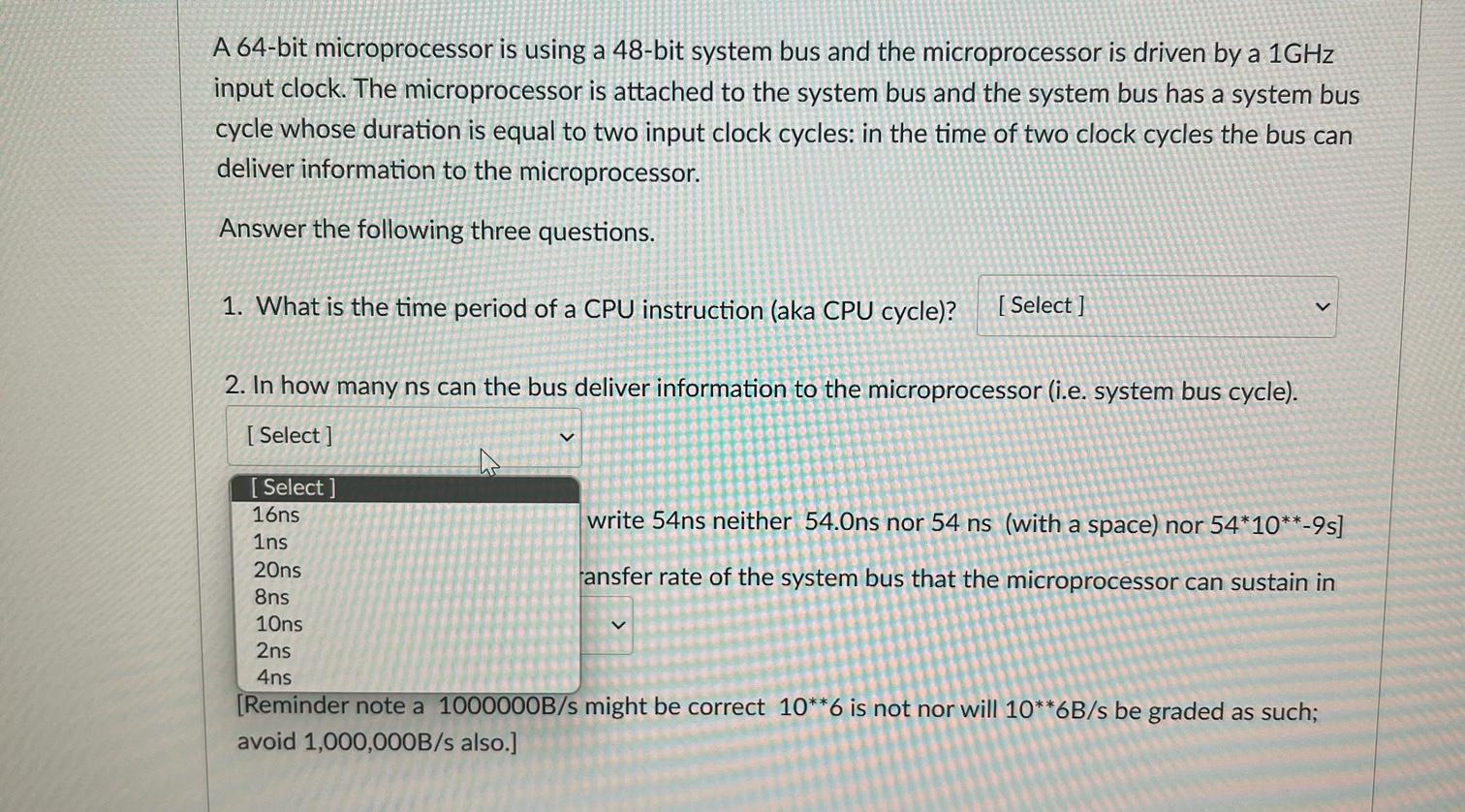

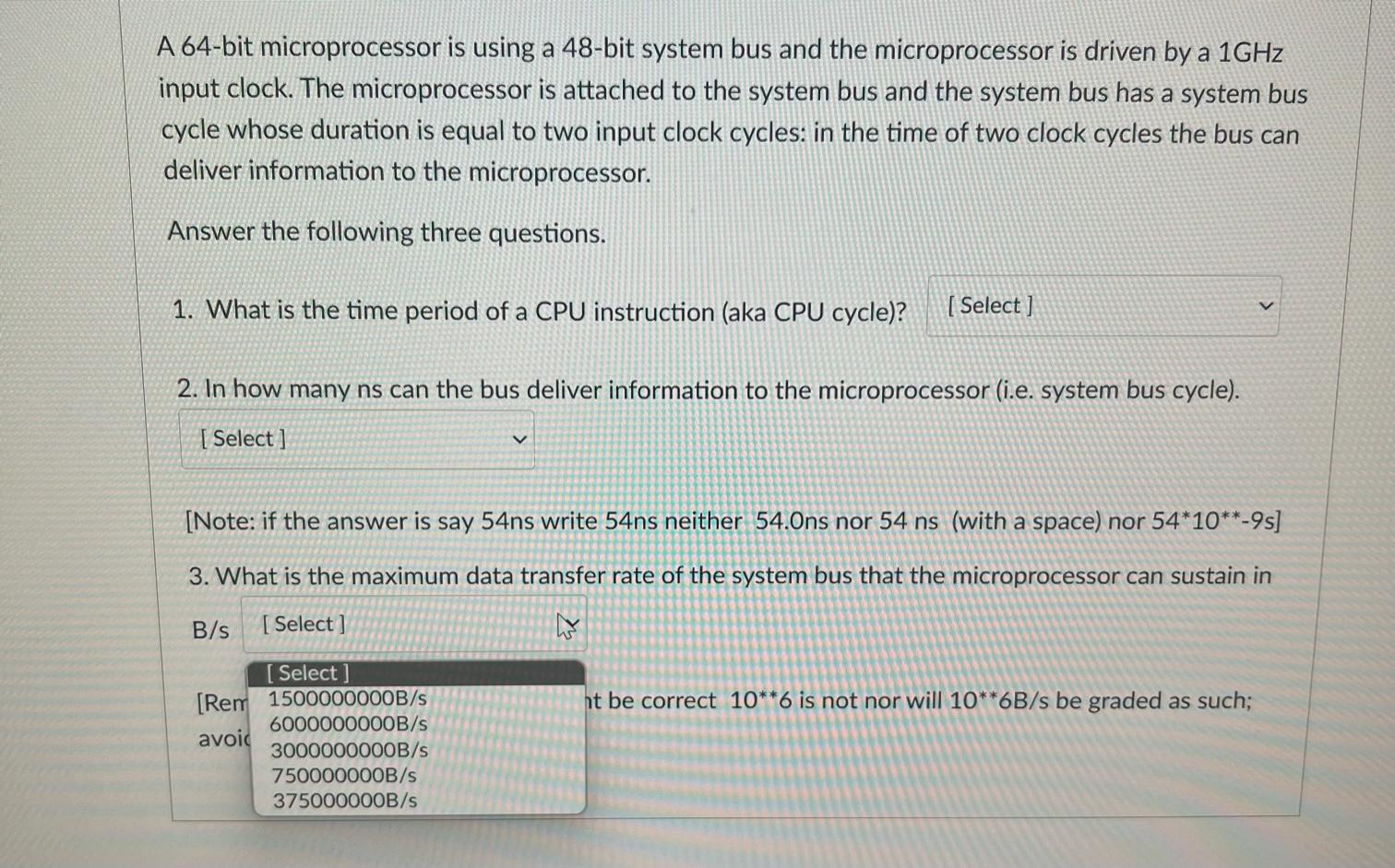

A 64-bit microprocessor is using a 48-bit system bus and the microprocessor is driven by a 1GHz input clock. The microprocessor is attached to the system bus and the system bus has a system bus cycle whose duration is equal to two input clock cycles: in the time of two clock cycles the bus can deliver information to the microprocessor. Answer the following three questions. 1. What is the time period of a CPU instruction (aka CPU cycle)? 2. In how many ns can the bus deliver information to the micropror [Note: if the answer is say 54ns write 54ns neither 54.0 ns nor 54 3. What is the maximum data transfer rate of the system bus that the microprocessor can sustain in B/s [Reminder note a 1000000B/s might be correct 106 is not nor will 106B/s be graded as such; avoid 1,000,000B/s also.] A 64-bit microprocessor is using a 48-bit system bus and the microprocessor is driven by a 1GHz input clock. The microprocessor is attached to the system bus and the system bus has a system bus cycle whose duration is equal to two input clock cycles: in the time of two clock cycles the bus can deliver information to the microprocessor. Answer the following three questions. 1. What is the time period of a CPU instruction (aka CPU cycle)? 2. In how many ns can the bus deliver information to the microprocessor (i.e. system bus cycle). write 54ns neither 54.0ns nor 54 ns (with a space) nor 54109s] ansfer rate of the system bus that the microprocessor can sustain in IReminaer note a IU0U0U0B/s might be correct 106 is not nor will 106B/s be graded as such; avoid 1,000,000B/s also.] A 64-bit microprocessor is using a 48-bit system bus and the microprocessor is driven by a 1GHz input clock. The microprocessor is attached to the system bus and the system bus has a system bus cycle whose duration is equal to two input clock cycles: in the time of two clock cycles the bus can deliver information to the microprocessor. Answer the following three questions. 1. What is the time period of a CPU instruction (aka CPU cycle)? 2. In how many ns can the bus deliver information to the microprocessor (i.e. system bus cycle). [Note: if the answer is say 54ns write 54ns neither 54.0ns nor 54 ns (with a space) nor 54109s ] 3. What is the maximum data transfer rate of the system bus that the microprocessor can sustain in B/s [Re t be correct 106 is not nor will 106B/s be graded as such

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts