Question: A) (7 pts) Assume the processor has full forwarding paths (including half-cycle write back), has stall capability based on non-forwardable data hazard detection, and resolves

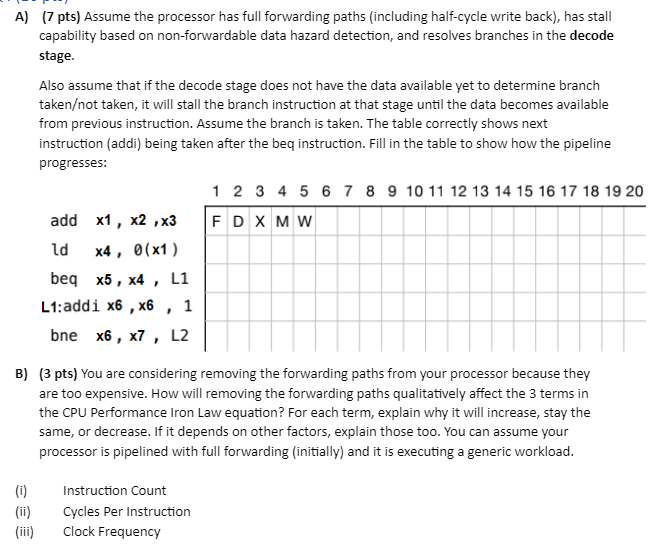

A) (7 pts) Assume the processor has full forwarding paths (including half-cycle write back), has stall capability based on non-forwardable data hazard detection, and resolves branches in the decode stage. Also assume that if the decode stage does not have the data available yet to determine branch takenot taken, it will stall the branch instruction at that stage until the data becomes available from previous instruction. Assume the branch is taken. The table correctly shows next instruction (addi) being taken after the beq instruction. Fill in the table to show how the pipeline progresses: B) ( 3 pts) You are considering removing the forwarding paths from your processor because they are too expensive. How will removing the forwarding paths qualitatively affect the 3 terms in the CPU Performance Iron Law equation? For each term, explain why it will increase, stay the same, or decrease. If it depends on other factors, explain those too. You can assume your processor is pipelined with full forwarding (initially) and it is executing a generic workload. (i) Instruction Count (ii) Cycles Per Instruction (iii) Clock Frequency

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts