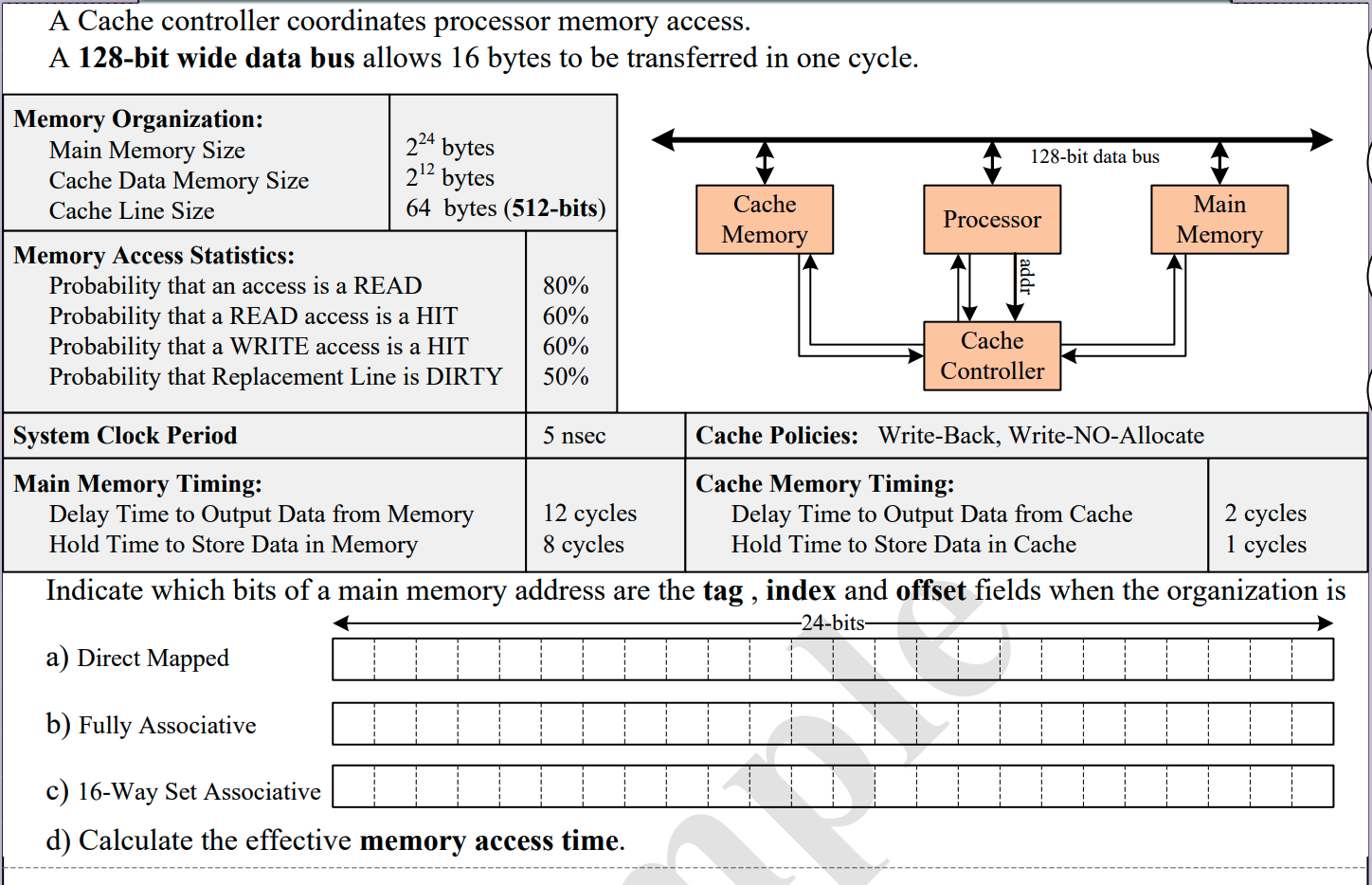

Question: A Cache controller coordinates processor memory access. A 128-bit wide data bus allows 16 bytes to be transferred in one cycle. 224 bytes 212 bytes

A Cache controller coordinates processor memory access. A 128-bit wide data bus allows 16 bytes to be transferred in one cycle. 224 bytes 212 bytes addr Memory Organization: Main Memory Size 128-bit data bus Cache Data Memory Size Cache Main Cache Line Size 64 bytes (512-bits) Processor Memory Memory Memory Access Statistics: Probability that an access is a READ 80% Probability that a READ access is a HIT 60% Probability that a WRITE access is a HIT 60% Cache Probability that Replacement Line is DIRTY 50% Controller System Clock Period 5 nsec Cache Policies: Write-Back, Write-NO-Allocate Main Memory Timing: Cache Memory Timing: Delay Time to Output Data from Memory 12 cycles Delay Time to Output Data from Cache 2 cycles Hold Time to Store Data in Memory 8 cycles Hold Time to Store Data in Cache 1 cycles Indicate which bits of a main memory address are the tag , index and offset fields when the organization is -24-bits- a) Direct Mapped b) Fully Associative c) 16-Way Set Associative d) Calculate the effective memory access time

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts