Question: A) Concisely write the Verilog code module for the controller part of a sequential system according to the given figures (Fig. 1 and Fig. 2).

A) Concisely write the Verilog code module for the controller part of a sequential system according to the given figures (Fig. 1 and Fig. 2).

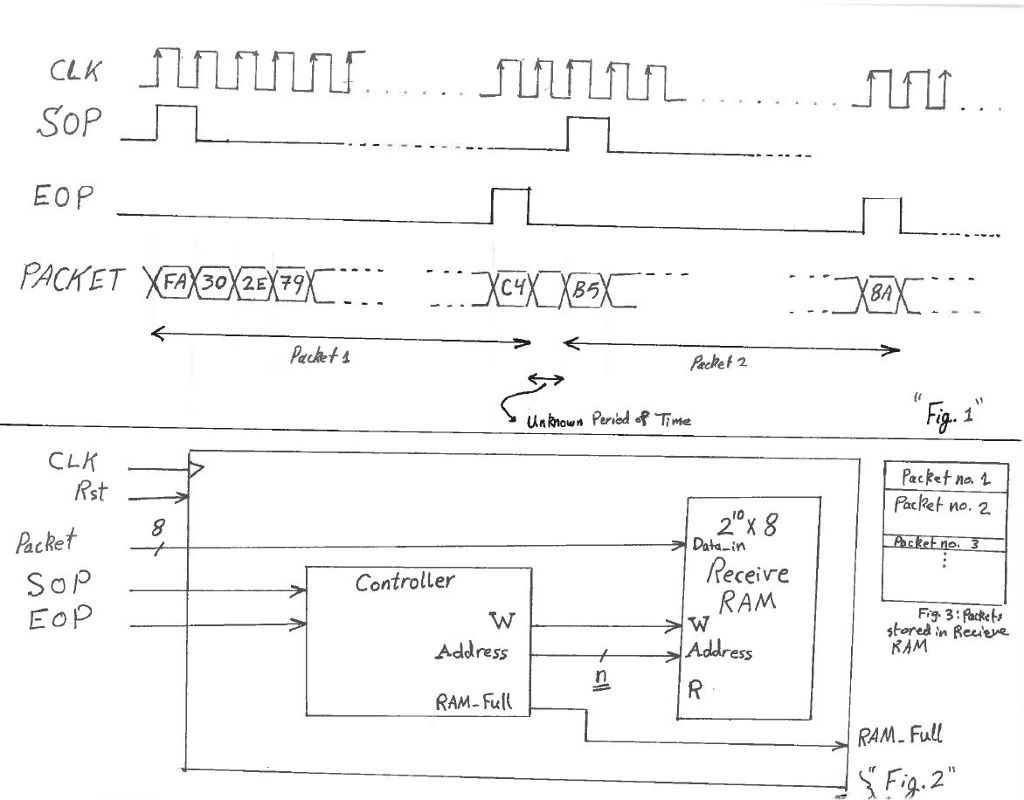

Stream of Packets arrive to the system to be stored in the Receive RAM (as shown in Fig.2). The packet arrives as a sequence of 8-bit data per clock at Packet input line (as shown in Fig. 1). Two signals are used to determine the beginning of a packet and end of a packet. SOP (Fig.1) indicates that a new packet has arrived to the system and need to be stored (8-bit per clock), and EOP (Fig. 1) indicates that the last byte of a packet has arrived, and then the write operation (storing in the RAM) has to be stopped. And the controller should wait for a new packet.

The size of each packet is unknown (e.g.; packet 1 could be 100 bytes, packet 2 could be 157 bytes, etc.), and the time between arriving packets is also unknown (as shown in Fig.

It is the controller responsibility to make a decision when writing to the Receive RAM should occur, or holding the write operation. The controller should also wait for a new packet to arrive to store it starting at the next memory location (Fig. 3). When the Receive RAM gets full, a RAM_FULL signal should be turned high. (note: do not overwrite on already stored data, because we assume another process will empty the Receive RAM). (Assume total size of packets will fit in 210 locations).

B) Find the value of n in Fig. 2.

C) Assume CLK =125MHz, what is the system input throughput (Bits/second)?.

CLK SoP EOP PACKET FX2 BA Packet 2 unknown Peried ime Fig. 1 CLA Packet no 1 Packet no. 2 Rst 10 8 2%8 Packet Data in eceive RAM Controller Address stored in Reciee RAM Address RAM- Ful RAM. Full Fig. 2 CLK SoP EOP PACKET FX2 BA Packet 2 unknown Peried ime Fig. 1 CLA Packet no 1 Packet no. 2 Rst 10 8 2%8 Packet Data in eceive RAM Controller Address stored in Reciee RAM Address RAM- Ful RAM. Full Fig. 2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts