Question: (a) Explain how an I-type load instruction would execute in this pipelined implementation. Show clearly that the result is written back in the proper Destination

(a) Explain how an I-type load instruction would execute in this pipelined implementation. Show clearly that the result is written back in the proper Destination Register.

(b) Define data dependency hazards and explain why they may occur in this implementation.

(c) Show that a memory write (store) instruction cannot cause a data dependency hazard.

(d) Can a store instruction be part of a data dependency hazard? Explain your answer.

(e) Considering R, I and J-type instructions, explain how to detect data dependency hazards for all possible instruction-type sequences

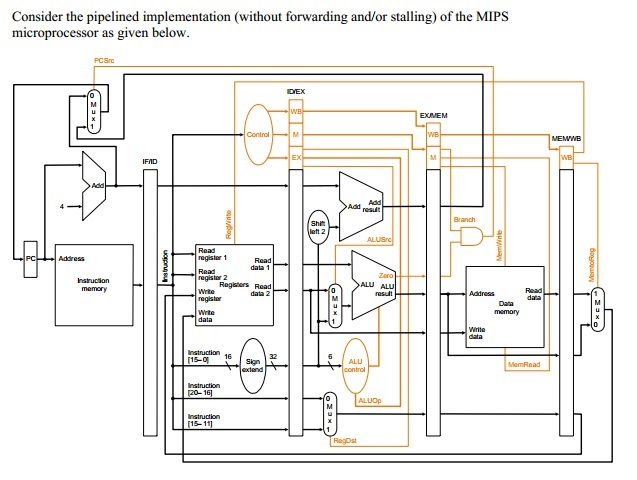

Consider the pipelined implementation (without forwarding and/or stalling) of the MIPS microprocessor as given below. register 1 register Registers Road register Consider the pipelined implementation (without forwarding and/or stalling) of the MIPS microprocessor as given below. register 1 register Registers Road register

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts