Question: A first level cache with access time of 1 clock cycle, and a miss rate of 3% is used in a computer with clock rate

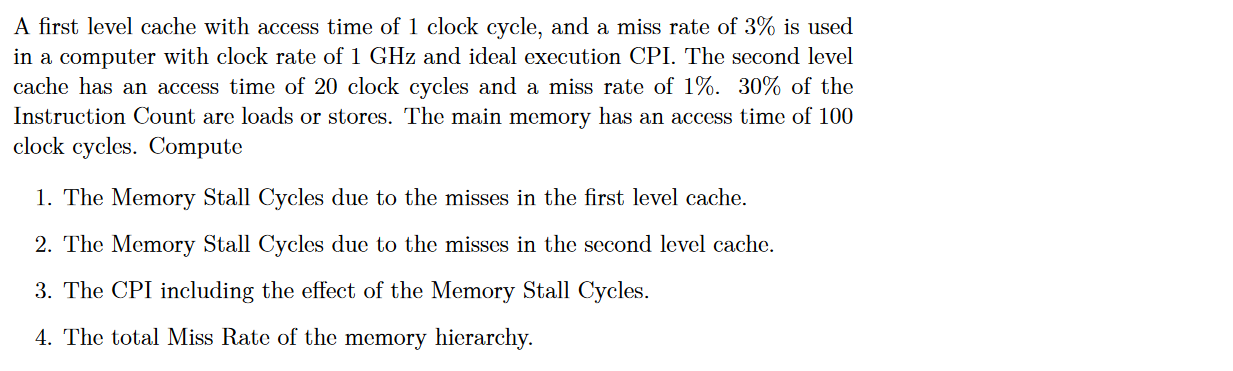

A first level cache with access time of 1 clock cycle, and a miss rate of 3% is used in a computer with clock rate of 1 GHz and ideal execution CPI. The second level cache has an access time of 20 clock cycles and a miss rate of 1%. 30% of the Instruction Count are loads or stores. The main memory has an access time of 100 clock cycles. Compute 1. The Memory Stall Cycles due to the misses in the first level cache. 2. The Memory Stall Cycles due to the misses in the second level cache. 3. The CPI including the effect of the Memory Stall Cycles. 4. The total Miss Rate of the memory hierarchy

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts