Question: Q1 A parallel adder has been introduced in Chapter 3. A parallel adder is fast, but complex and high in cost. Hence, for some

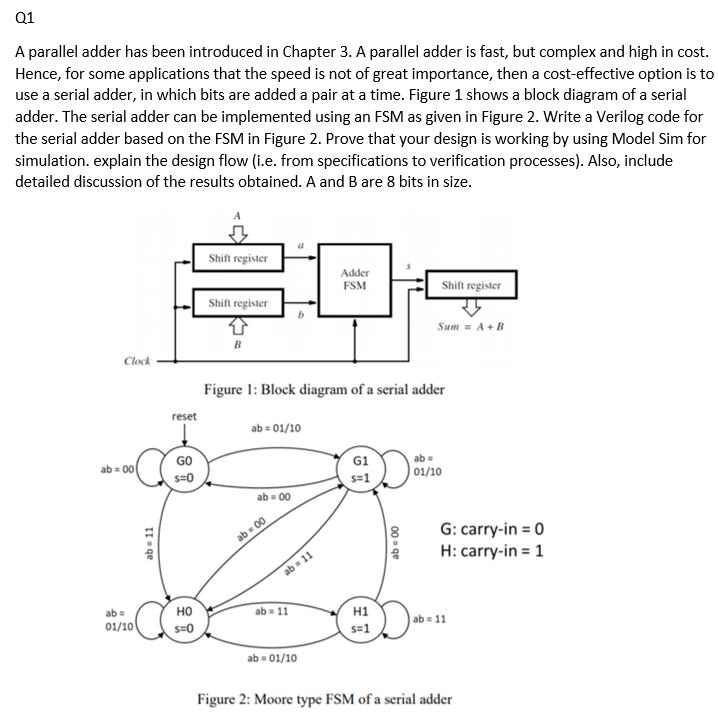

Q1 A parallel adder has been introduced in Chapter 3. A parallel adder is fast, but complex and high in cost. Hence, for some applications that the speed is not of great importance, then a cost-effective option is to use a serial adder, in which bits are added a pair at a time. Figure 1 shows a block diagram of a serial adder. The serial adder can be implemented using an FSM as given in Figure 2. Write a Verilog code for the serial adder based on the FSM in Figure 2. Prove that your design is working by using Model Sim for simulation. explain the design flow (i.e. from specifications to verification processes). Also, include detailed discussion of the results obtained. A and B are 8 bits in size. Shift register Adder FSM Shift register Shift register Sum = A+B B Clock Figure 1: Block diagram of a serial adder reset ab = 01/10 GO ab = 00 G1 ab= s=0 s=1 01/10 ab = 00 G: carry-in = 0 H: carry-in = 1 ab = 00 ab = 11 ab = ab = 11 H1 01/10 s=0 |ab = 11 s=1 ab = 01/10 Figure 2: Moore type FSM of a serial adder ab 11 00 - qe

Step by Step Solution

There are 3 Steps involved in it

moore FSM for the following is shown below using verilog ... View full answer

Get step-by-step solutions from verified subject matter experts