Question: A processor has separate instruction and data caches, each requiring two cycles for any operation. It includes a single 2-cycles execution unit responsible for executing

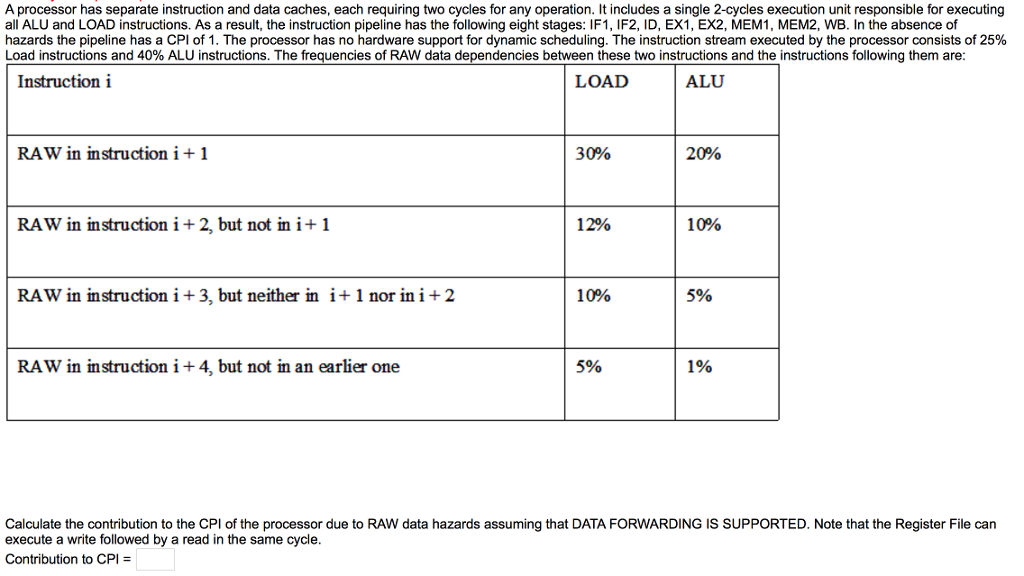

A processor has separate instruction and data caches, each requiring two cycles for any operation. It includes a single 2-cycles execution unit responsible for executing all ALU and LOAD instructions. As a result, the instruction pipeline has the following eight stages: IF1, IF2, ID, EX1, EX2, MEM1, MEM2, WB. In the absence of hazards the pipeline has a CPI of 1. The processor has no hardware support for dynamic scheduling. The instruction stream executed by the processor consists of 25% Load instructions and 40% ALU instructions. The frequencies of RAW data dependencies between these two instructions and the instructions following them are: Instruction i LOAD ALU RAW in instruction i +1 30% 20% RAW in instruction i +2, but not in i+ 1 12% 10% RAW in instruction i +3, but neither in i+ 1 nor in i +2 10% 5% RAW in instructioni+ 4, but not in an earlier one 5% 1% Calculate the contribution to the CPI of the processor due to RAW data hazards assuming that DATA FORWARDING IS SUPPORTED. Note that the Register File can execute a write followed by a read in the same cycle. Contribution to CPI = A processor has separate instruction and data caches, each requiring two cycles for any operation. It includes a single 2-cycles execution unit responsible for executing all ALU and LOAD instructions. As a result, the instruction pipeline has the following eight stages: IF1, IF2, ID, EX1, EX2, MEM1, MEM2, WB. In the absence of hazards the pipeline has a CPI of 1. The processor has no hardware support for dynamic scheduling. The instruction stream executed by the processor consists of 25% Load instructions and 40% ALU instructions. The frequencies of RAW data dependencies between these two instructions and the instructions following them are: Instruction i LOAD ALU RAW in instruction i +1 30% 20% RAW in instruction i +2, but not in i+ 1 12% 10% RAW in instruction i +3, but neither in i+ 1 nor in i +2 10% 5% RAW in instructioni+ 4, but not in an earlier one 5% 1% Calculate the contribution to the CPI of the processor due to RAW data hazards assuming that DATA FORWARDING IS SUPPORTED. Note that the Register File can execute a write followed by a read in the same cycle. Contribution to CPI =

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts