Question: A processor instruction pipeline with k stages gets to stall 5% of the time due to data dependence. In addition, 5% of the instructions are

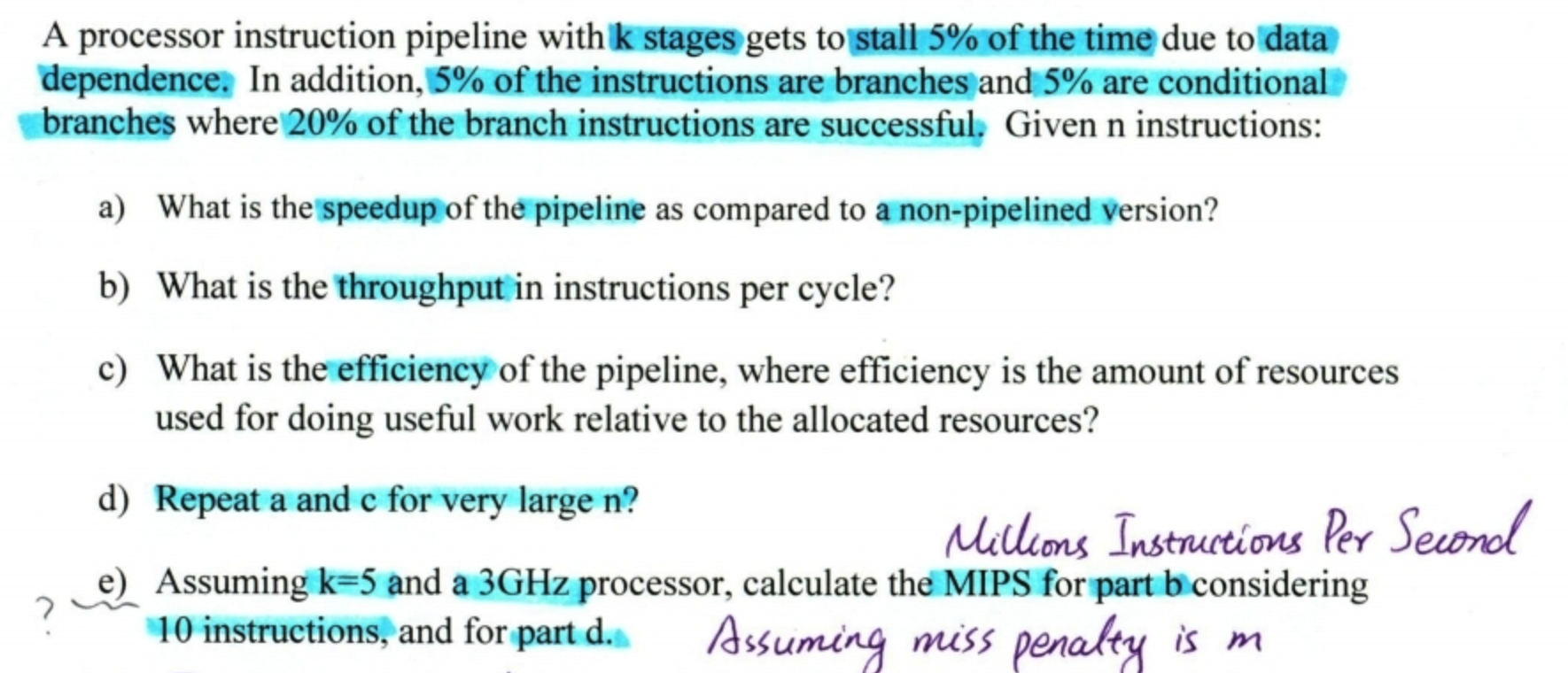

A processor instruction pipeline with k stages gets to stall 5% of the time due to data dependence. In addition, 5% of the instructions are branches and 5% are conditional branches where 20% of the branch instructions are successful. Given n instructions: a) What is the speedup of the pipeline as compared to a non-pipelined version? b) What is the throughput in instructions per cycle? c) What is the efficiency of the pipeline, where efficiency is the amount of resources used for doing useful work relative to the allocated resources? d) Repeat a and c for very large n? Millions Instructions Per Second Assuming k=5 and a 3GHz processor, calculate the MIPS for part b considering 10 instructions, and for part d. Assuming miss penalty is m A processor instruction pipeline with k stages gets to stall 5% of the time due to data dependence. In addition, 5% of the instructions are branches and 5% are conditional branches where 20% of the branch instructions are successful. Given n instructions: a) What is the speedup of the pipeline as compared to a non-pipelined version? b) What is the throughput in instructions per cycle? c) What is the efficiency of the pipeline, where efficiency is the amount of resources used for doing useful work relative to the allocated resources? d) Repeat a and c for very large n? Millions Instructions Per Second Assuming k=5 and a 3GHz processor, calculate the MIPS for part b considering 10 instructions, and for part d. Assuming miss penalty is m

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts