Question: A sequential circuit is required that can generate an even parity for a sequence of 5 - bit binary data. The 5 - bit binary

A sequential circuit is required that can generate an even parity for a

sequence of bit binary data. The bit binary number is available on a

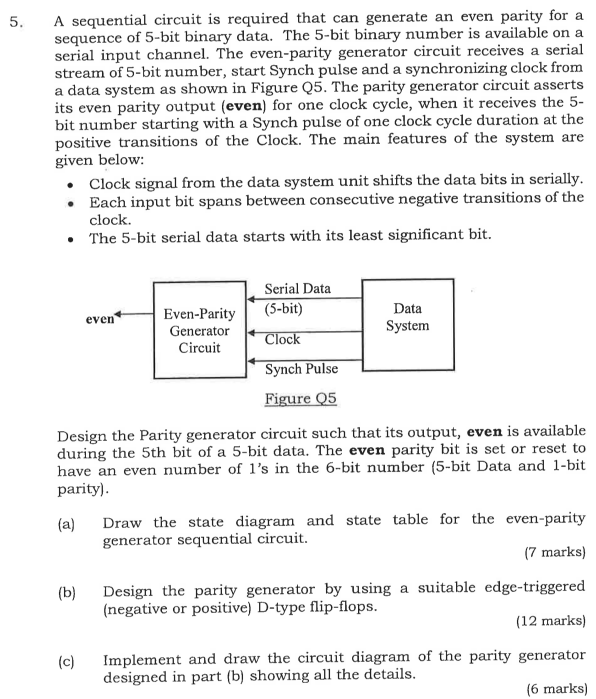

serial input channel. The evenparity generator circuit receives a serial

stream of bit number, start Synch pulse and a synchronizing clock from

a data system as shown in Figure Q The parity generator circuit asserts

its even parity output even for one clock cycle, when it receives the

bit number starting with a Synch pulse of one clock cycle duration at the

positive transitions of the Clock. The main features of the system are

given below:

Clock signal from the data system unit shifts the data bits in serially.

Each input bit spans between consecutive negative transitions of the

clock.

The bit serial data starts with its least significant bit.

Design the Parity generator circuit such that its output, even is available

during the th bit of a bit data. The even parity bit is set or reset to

have an even number of s in the bit number bit Data and bit

parity

a Draw the state diagram and state table for the evenparity

generator sequential circuit.

marks

b Design the parity generator by using a suitable edgetriggered

negative or positive Dtype flipflops.

marks

c Implement and draw the circuit diagram of the parity generator

designed in part b showing all the details.

marks

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock