Question: A silicon p-channel (n-substrate) MOS capacitor has a polysilicon gate heavily doped such that its Ey = Er. Its n-type substrate has a doping of

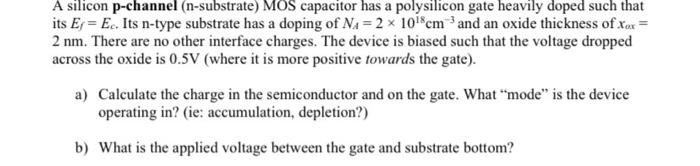

A silicon p-channel (n-substrate) MOS capacitor has a polysilicon gate heavily doped such that its Ey = Er. Its n-type substrate has a doping of MA = 2 x 10"cm and an oxide thickness of Xox = 2 nm. There are no other interface charges. The device is biased such that the voltage dropped across the oxide is 0.5V (where it is more positive towards the gate). a) Calculate the charge in the semiconductor and on the gate. What "mode" is the device operating in? (ie: accumulation, depletion?) b) What is the applied voltage between the gate and substrate bottom

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock