Question: Adder Subtractor for signed numbers with Overflow detector A, B, X, Y, S, Z represent 4-bit numbers in 2's complement form. Note that the range

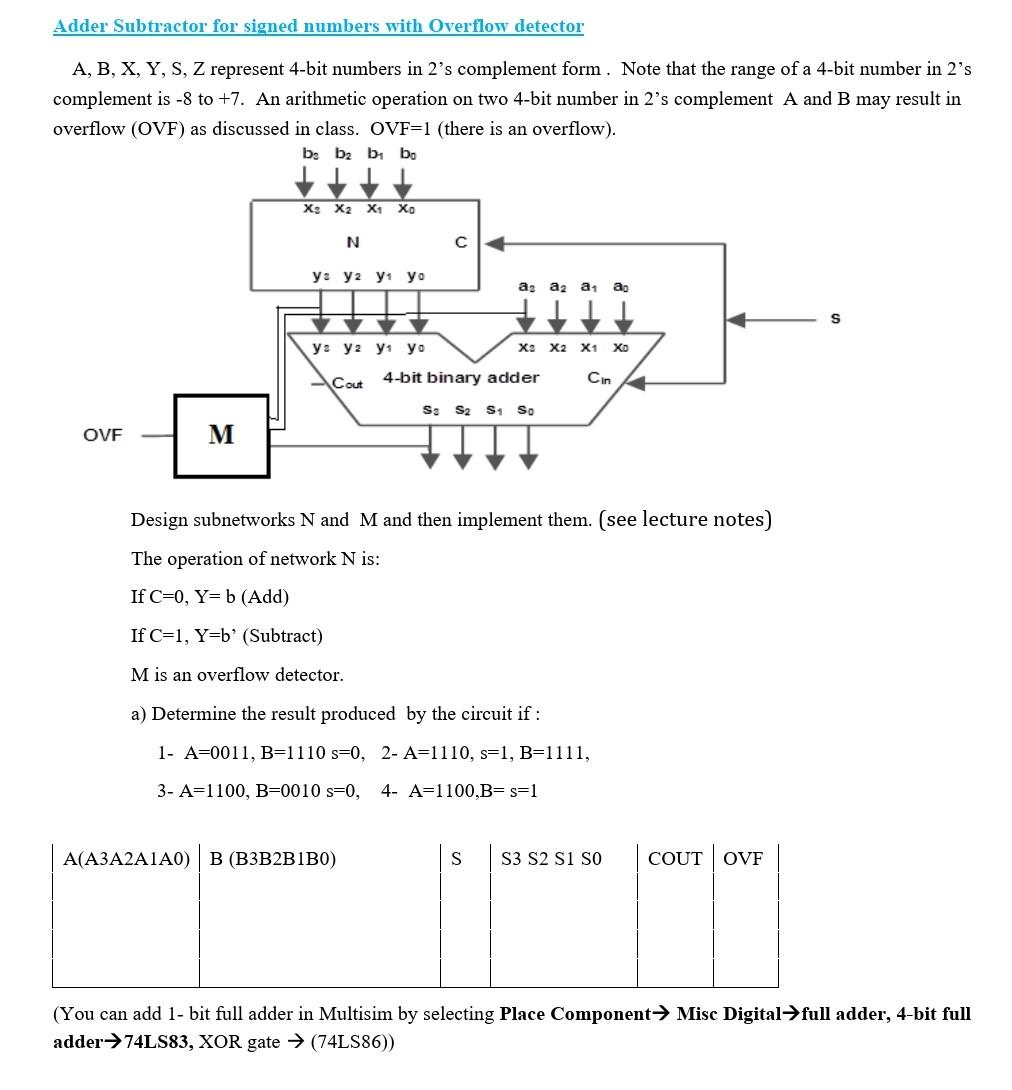

Adder Subtractor for signed numbers with Overflow detector A, B, X, Y, S, Z represent 4-bit numbers in 2's complement form. Note that the range of a 4-bit number in 2's complement is -8 to +7. An arithmetic operation on two 4-bit number in 2's complement A and B may result in overflow (OVF) as discussed in class. OVF=1 (there is an overflow). ba ba bi bo 11 1 VVV X3 X2 X1 Xo N y: y2 + yo az a2 a ao yy2 y yo X: X2 X1 Xo Cout 4-bit binary adder Cin S3 S2 S1 So OVE M Design subnetworks N and M and then implement them. (see lecture notes) The operation of network N is: If C=0, Y=b (Add) If C=1, Y=b' (Subtract) M is an overflow detector. a) Determine the result produced by the circuit if : 1- A=0011, B=1110 s=0, 2-A=1110, s=1, B=1111, 3- A=1100, B=0010 s=0, 4- A=1100,B=s=1 A(A3A2A1A0) B (B3B2B1BO) S S3 S2 S1 SO COUT OVF (You can add 1- bit full adder in Multisim by selecting Place Component Misc Digitalfull adder, 4-bit full adder 74LS83, XOR gate (74LS86)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts