Question: Algorithm Loops. A Control Unit and Datapath are designed to act as a simple loop counter. The Datapath contains a register that down - counts

Algorithm Loops.

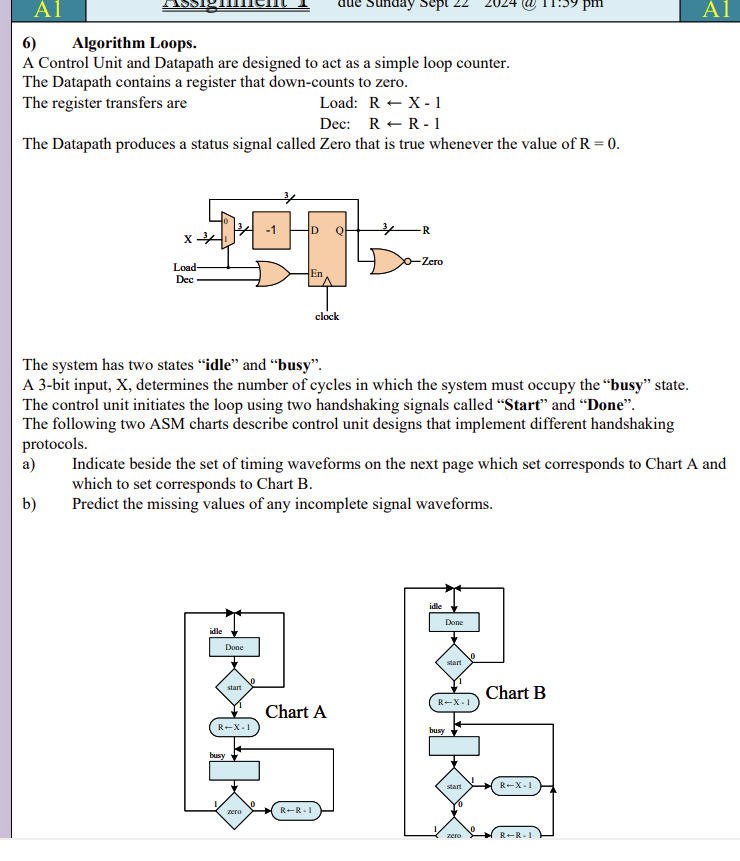

A Control Unit and Datapath are designed to act as a simple loop counter.

The Datapath contains a register that downcounts to zero.

The register transfers are

Load: Rlarrx

Dec: RlarrR

The Datapath produces a status signal called Zero that is true whenever the value of

The system has two states "idle" and "busy".

A bit input, X determines the number of cycles in which the system must occupy the "busy" state.

The control unit initiates the loop using two handshaking signals called "Start" and "Done".

The following two ASM charts describe control unit designs that implement different handshaking

protocols.

a Indicate beside the set of timing waveforms on the next page which set corresponds to Chart A and

which to set corresponds to Chart B

b Predict the missing values of any incomplete signal waveforms. Algorithm Loops.

c Draw an ASM Chart for a Control Unit that implements the following protocol.

The Operand, X is guaranteed valid whenever Start

The counter, when busy, cannot be restarted until it has completed the correct number of "busy"

states.

The Done whenever the system is idle.

The system may start a new loop immediately upon completing a previous loop without

becoming idle in between.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock