Question: answer this question please subject High-Level VLSI Design Methodology HW2: Task-3 RTL programing Simplified CPU architecture SPEC: ALU Define your own instruction format (32bits) OP:

answer this question please

subject

| High-Level VLSI Design Methodology |

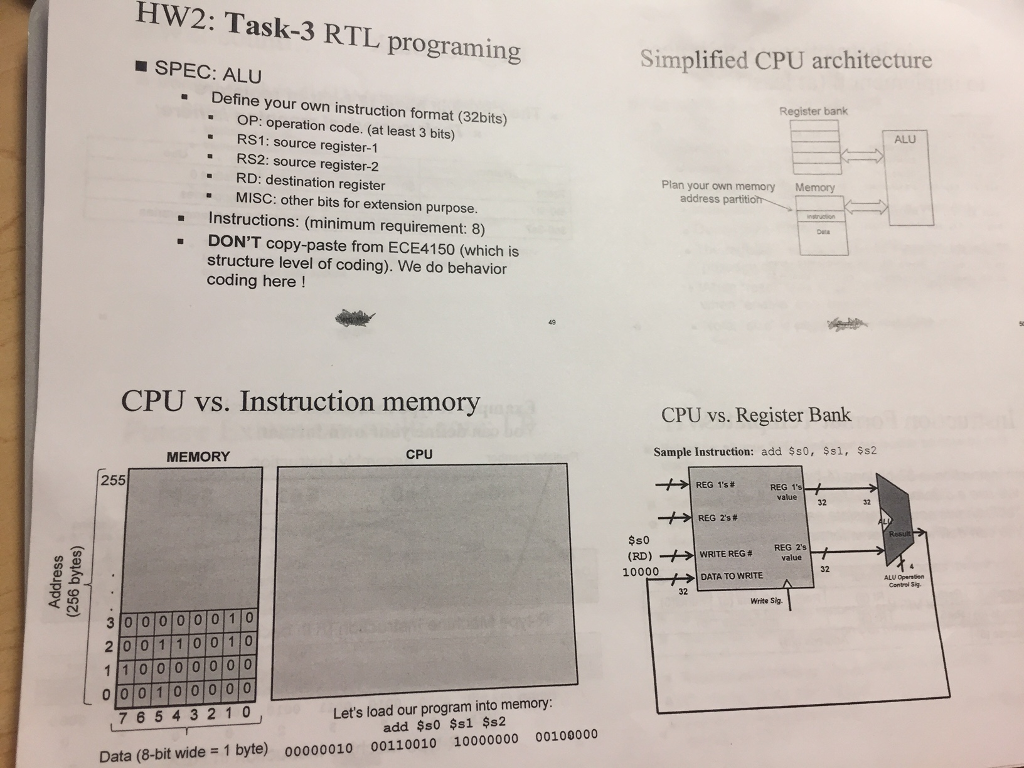

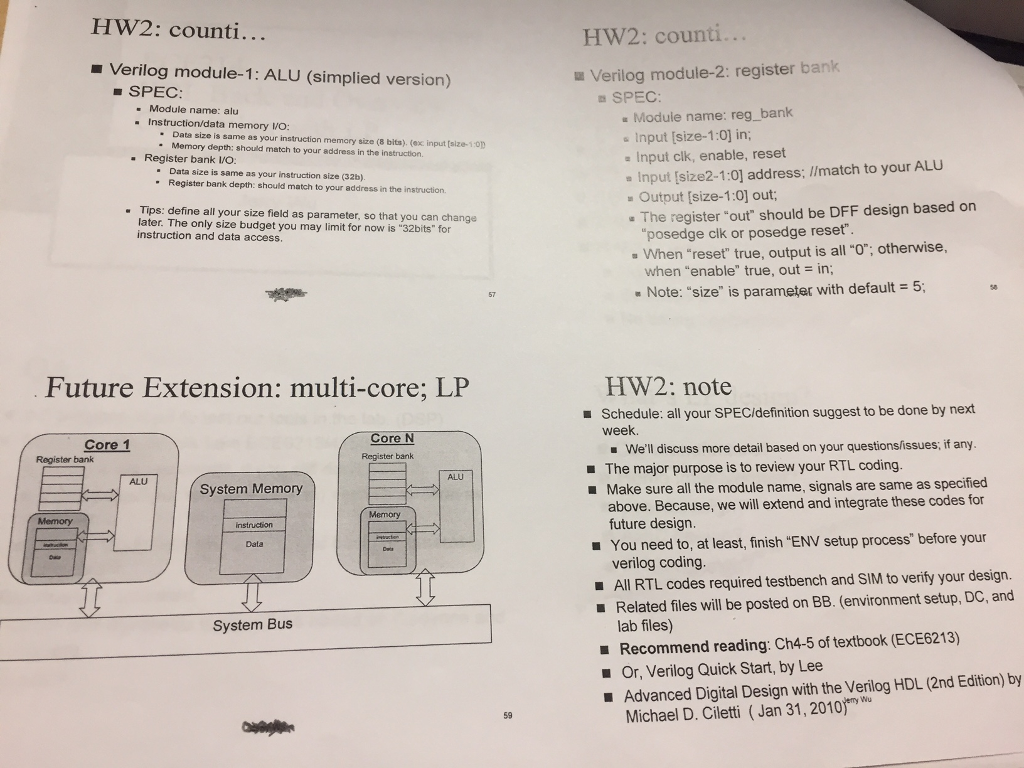

HW2: Task-3 RTL programing Simplified CPU architecture SPEC: ALU Define your own instruction format (32bits) OP: operation code. (at least 3 bits) Register bank RS1: source register-1 RS2: source ALU RD: destination register Plan your own memory Memory MISC: other bits for extension purpose. address partiti Instructions: (minimum requirement: 8) DON'T copy-paste from ECE4150 (which is structure level of coding). We do behavior coding here! CPU vs. Instruction memory CPU vs. Register Bank Sample Instruction: add $s0, $s1, $s2 CPU MEMORY 255 REG 1's REG 1's value 32, REG 2's REG 2's (RD) WRITE REG 10000 DATA TO WRITE Control Sig. Write Sig. 3 0 0 0 0 0 0 1 0 2 0 0 1 1 0 0 1 0 1 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 7 6 5 4 3 2 1 0 Let's load our program into memory: add $50 $s2 Data (8-bit wide 1 byte) 00000010 00110010 10000000 00100000

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts