Question: Assume a 5-bit virtual address and a memory system that uses 4 bytes per page. The physical memory has 16 bytes (four page frames). The

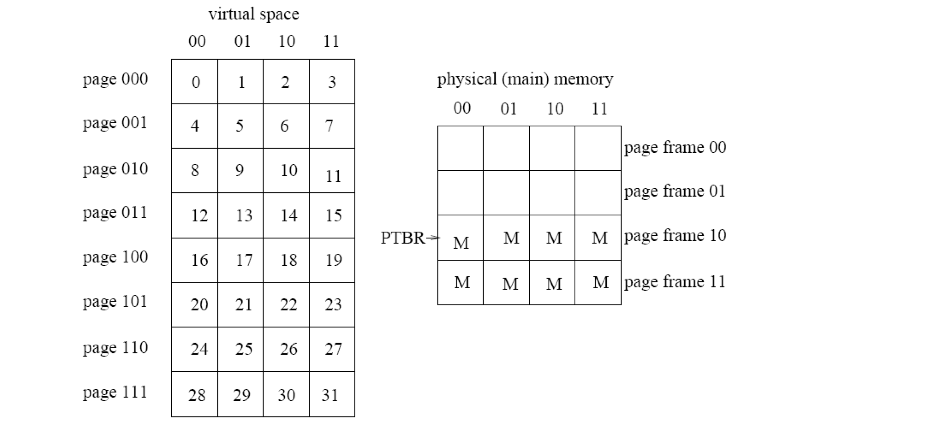

Assume a 5-bit virtual address and a memory system that uses 4 bytes per page. The physical memory has 16 bytes (four page frames). The TLB has two slots, and the page table used is a one-level scheme that can be found in memory at the page table base register (PTBR) location. Initially the table indicates that no virtual pages have been mapped. Implementing a FIFO policy for the TLB and LRU page replacement algorithm, show the contents of physical memory, the TLB, and the page table after the following virtual accesses: 10100, 01000, 00011, 01011, 01011, 11111. For each, also indicate when a page fault occurs. Each page table entry (PTE) is 1 byte.

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts