Question: Assume a CPU has the following instruction form: Op code [model operand1] [mode2 operand2] [mode3 operand3] The op code specifies the type of operation which

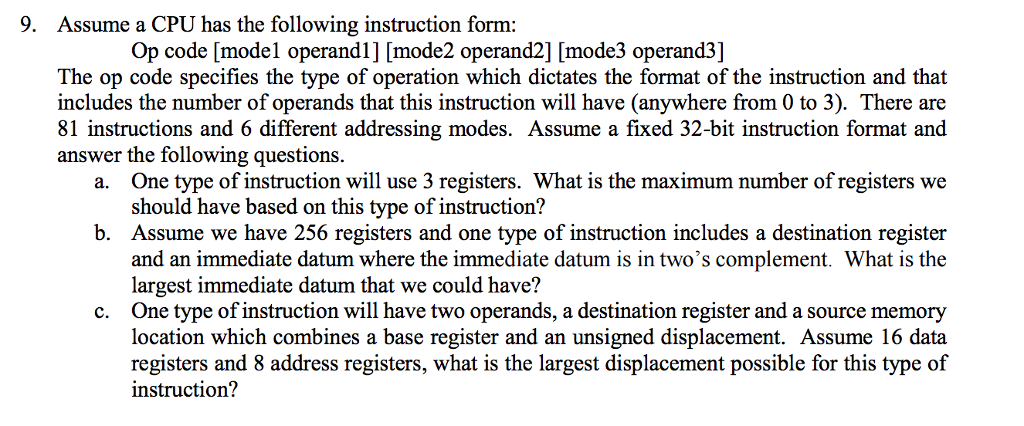

Assume a CPU has the following instruction form: Op code [model operand1] [mode2 operand2] [mode3 operand3] The op code specifies the type of operation which dictates the format of the instruction and that includes the number of operands that this instruction will have (anywhere from 0 to 3). There are 81 instructions and 6 different addressing modes. Assume a fixed 32-bit instruction format and answer the following questions. a. One type of instruction will use 3 registers. What is the maximum number of registers we should have based on this type of instruction? b. Assume we have 256 registers and one type of instruction includes a destination register and an immediate datum where the immediate datum is in two's complement. What is the largest immediate datum that we could have? c. One type of instruction will have two operands, a destination register and a source memory location which combines a base register and an unsigned displacement. Assume 16 data registers and 8 address registers, what is the largest displacement possible for this type of instruction? Assume a CPU has the following instruction form: Op code [model operand1] [mode2 operand2] [mode3 operand3] The op code specifies the type of operation which dictates the format of the instruction and that includes the number of operands that this instruction will have (anywhere from 0 to 3). There are 81 instructions and 6 different addressing modes. Assume a fixed 32-bit instruction format and answer the following questions. a. One type of instruction will use 3 registers. What is the maximum number of registers we should have based on this type of instruction? b. Assume we have 256 registers and one type of instruction includes a destination register and an immediate datum where the immediate datum is in two's complement. What is the largest immediate datum that we could have? c. One type of instruction will have two operands, a destination register and a source memory location which combines a base register and an unsigned displacement. Assume 16 data registers and 8 address registers, what is the largest displacement possible for this type of instruction

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts