Question: Assume a processor executes each instruction in 1000 picoseconds (ps). Assume they can be pipelined with an additional 10 ps overhead per pipeline stage due

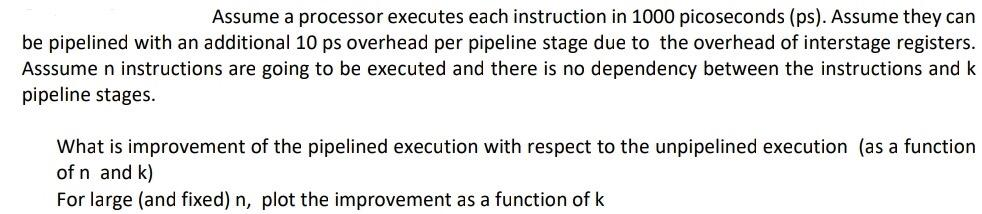

Assume a processor executes each instruction in 1000 picoseconds (ps). Assume they can be pipelined with an additional 10 ps overhead per pipeline stage due to the overhead of interstage registers. Asssume n instructions are going to be executed and there is no dependency between the instructions and k pipeline stages. What is improvement of the pipelined execution with respect to the unpipelined execution (as a function of n and k) For large (and fixed) n, plot the improvement as a function of k

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts