Question: Assume that an N-issue superscalar processor can execute any N instructions in the same cycle, regardless of their types. Second, assume that every instruction is

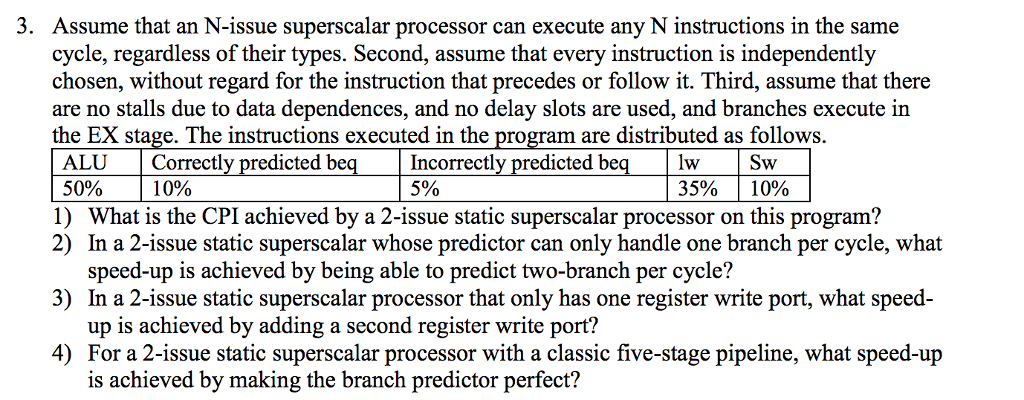

Assume that an N-issue superscalar processor can execute any N instructions in the same cycle, regardless of their types. Second, assume that every instruction is independently chosen, without regard for the instruction that precedes or follow it. Third, assume that there are no stalls due to data dependences, and no delay slots are used, and branches execute in the EX stage. The instructions executed in the program are distributed as follows. 1) What is the CPI achieved by a 2-issue static superscalar processor on this program? 2) In a 2-issue static superscalar whose predictor can only handle one branch per cycle, what speed-up is achieved by being able to predict two-branch per cycle? 3) In a 2-issue static superscalar processor that only has one register write port, what speed up is achieved by adding a second register write port? 4) For a 2-issue static superscalar processor with a classic five-stage pipeline, what speed-up is achieved by making the branch predictor perfect? Assume that an N-issue superscalar processor can execute any N instructions in the same cycle, regardless of their types. Second, assume that every instruction is independently chosen, without regard for the instruction that precedes or follow it. Third, assume that there are no stalls due to data dependences, and no delay slots are used, and branches execute in the EX stage. The instructions executed in the program are distributed as follows. 1) What is the CPI achieved by a 2-issue static superscalar processor on this program? 2) In a 2-issue static superscalar whose predictor can only handle one branch per cycle, what speed-up is achieved by being able to predict two-branch per cycle? 3) In a 2-issue static superscalar processor that only has one register write port, what speed up is achieved by adding a second register write port? 4) For a 2-issue static superscalar processor with a classic five-stage pipeline, what speed-up is achieved by making the branch predictor perfect

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts