Question: (b) Explain why the following SystemVerilog code might show different behaviour when simulated to that when synthesised. module two_ff (input logic clk, a, output logic

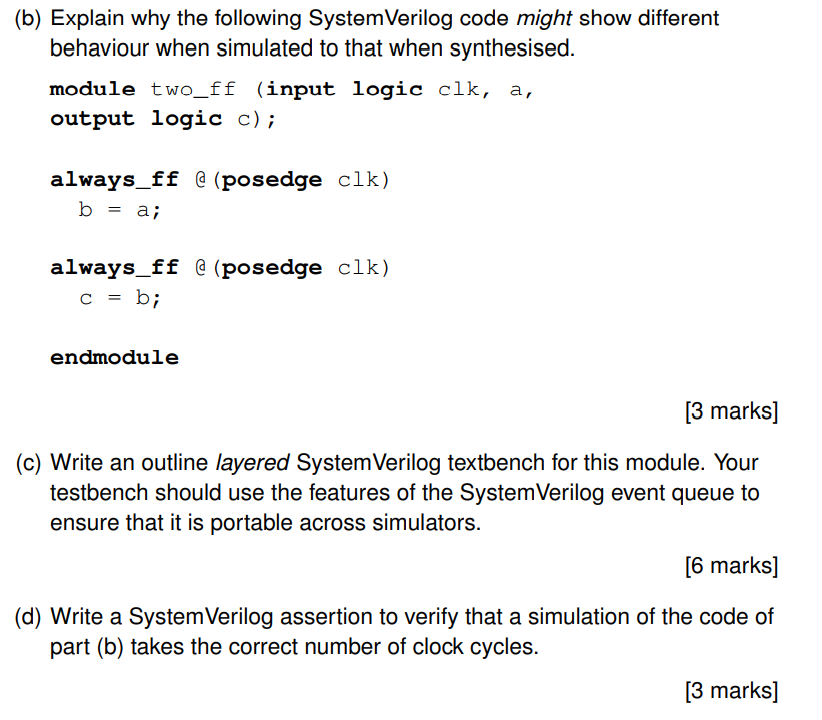

(b) Explain why the following SystemVerilog code might show different behaviour when simulated to that when synthesised. module two_ff (input logic clk, a, output logic c); always_ff a (posedge clk) b=a; always_ff @ (posedge clk) c=b; endmodule [3 marks] (c) Write an outline layered SystemVerilog textbench for this module. Your testbench should use the features of the SystemVerilog event queue to ensure that it is portable across simulators. [6 marks] (d) Write a SystemVerilog assertion to verify that a simulation of the code of part (b) takes the correct number of clock cycles. [3 marks]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts