Question: c) Add the following 4-bit signed (2's complement) numbers: 3+6. The result is stored in 4-bit word. What is the result? Did the overflow happen?

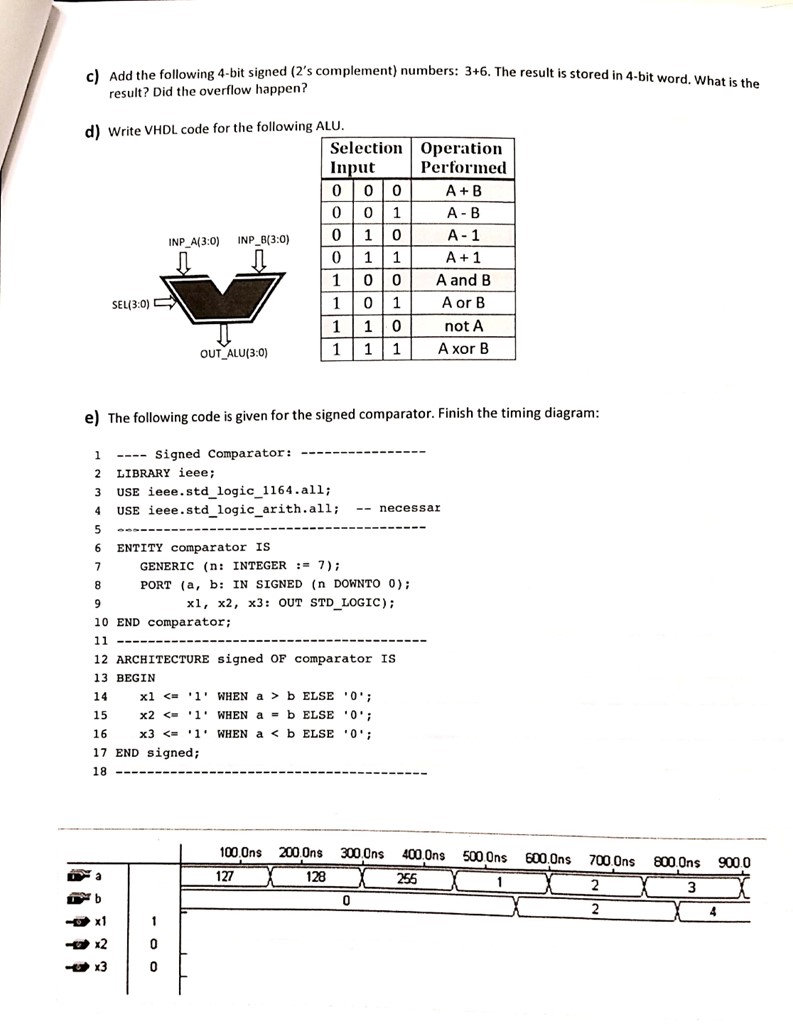

c) Add the following 4-bit signed (2's complement) numbers: 3+6. The result is stored in 4-bit word. What is the result? Did the overflow happen? d) Write VHDL code for the following AIII e) The following code is given for the signed comparator. Finish the timing diagram: ---- Signed Comparator: ------------------ LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; -- necessar ENTITY comparator IS GENERIC (n: INTEGER := 7); PORT (a, b: IN SIGNED ( n DOWNTO 0); x1,x2,x3 : OUT STD_LOGIC); END comparator; ARCHITECTURE signed OF comparator IS BEGIN x1b ELSE ' 0 '; x2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts