Question: Cache Layout: A processor has a separate D-cache and an I-cache. D-cache: 64KB, 4-way set associative, block size of 1 word, write-back policy I-cache:

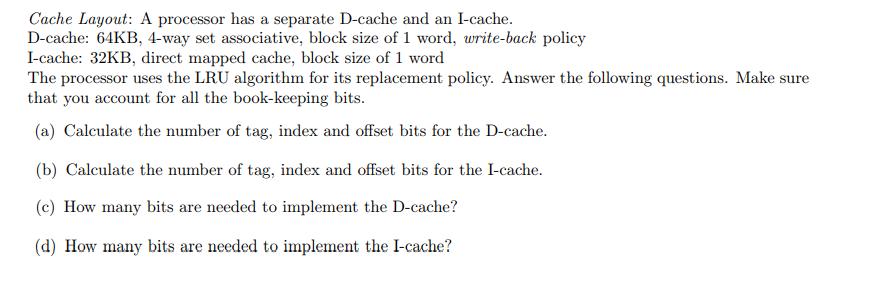

Cache Layout: A processor has a separate D-cache and an I-cache. D-cache: 64KB, 4-way set associative, block size of 1 word, write-back policy I-cache: 32KB, direct mapped cache, block size of 1 word The processor uses the LRU algorithm for its replacement policy. Answer the following questions. Make sure that you account for all the book-keeping bits. (a) Calculate the number of tag, index and offset bits for the D-cache. (b) Calculate the number of tag, index and offset bits for the I-cache. (c) How many bits are needed to implement the D-cache? (d) How many bits are needed to implement the I-cache?

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts