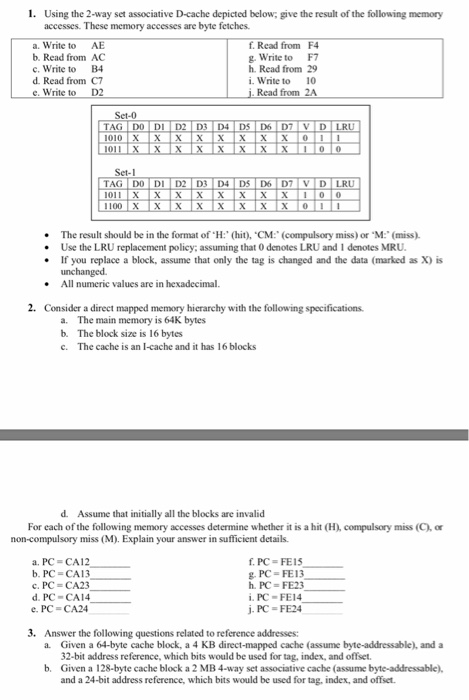

Question: Assignment: 1. Using the 2-way set associative D-cache depicted below; give the result of the following memory accesses. These memory accesses are byte fetches a.

1. Using the 2-way set associative D-cache depicted below; give the result of the following memory accesses. These memory accesses are byte fetches a. Write to A b. Read from AC c. Write to B4 d. Read from C7 e. Write to D2 f. Read from F4 g. Write to F7 h. Read from 29 i. Write to 10 Read from 2 Set-0 TAG | DO | DI | 1010 D3 Set-I TAG | Do | DI 1011 100 .The result should be in the format of "H:(hit), CM: (compulsory miss) or M: (miss). . Use the LRU replacement policy; assuming that 0 denotes LRU and 1 denotes MRU. .If you replace a block, assume that only the tag is changed and the data (marked as X) is unchanged. All numeric values are in hexadecimal. 2. Consider a direct mapped memory hierarchy with the following specifications. a. b. c. The main memory is 64K bytes The block size is 16 bytes The cache is an I-cache and it has 16 blocks d. Assume that initially all the blocks are invalid For each of the following memory accesses determine whether it is a hit (H), compulsory miss (C), or non-compulsory miss (M). Explain your answer in sufficient details a. PC- CA12 b. PC-CA13 c. PC- CA23 d. PC- CA14 e. PC CA24 . PC- FE1S g. PC-FE13 h. PC- FE23 i. PC-FE14 j. PC FE24 3. Answer the following questions related to reference addresses: a. Given a 64-byte cache block, a 4 KB direct-mapped cache (assume byte-addressable), and a 32-bit address reference, which bits would be used for tag, index, and offset. Given a 128-byte cache block a 2 MB 4-way set associative cache (assume byte-addressable), and a 24-bit address reference, which bits would be used for tag, index, and offset b. 1. Using the 2-way set associative D-cache depicted below; give the result of the following memory accesses. These memory accesses are byte fetches a. Write to A b. Read from AC c. Write to B4 d. Read from C7 e. Write to D2 f. Read from F4 g. Write to F7 h. Read from 29 i. Write to 10 Read from 2 Set-0 TAG | DO | DI | 1010 D3 Set-I TAG | Do | DI 1011 100 .The result should be in the format of "H:(hit), CM: (compulsory miss) or M: (miss). . Use the LRU replacement policy; assuming that 0 denotes LRU and 1 denotes MRU. .If you replace a block, assume that only the tag is changed and the data (marked as X) is unchanged. All numeric values are in hexadecimal. 2. Consider a direct mapped memory hierarchy with the following specifications. a. b. c. The main memory is 64K bytes The block size is 16 bytes The cache is an I-cache and it has 16 blocks d. Assume that initially all the blocks are invalid For each of the following memory accesses determine whether it is a hit (H), compulsory miss (C), or non-compulsory miss (M). Explain your answer in sufficient details a. PC- CA12 b. PC-CA13 c. PC- CA23 d. PC- CA14 e. PC CA24 . PC- FE1S g. PC-FE13 h. PC- FE23 i. PC-FE14 j. PC FE24 3. Answer the following questions related to reference addresses: a. Given a 64-byte cache block, a 4 KB direct-mapped cache (assume byte-addressable), and a 32-bit address reference, which bits would be used for tag, index, and offset. Given a 128-byte cache block a 2 MB 4-way set associative cache (assume byte-addressable), and a 24-bit address reference, which bits would be used for tag, index, and offset b

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts