Question: Can someone please show me the steps and explain how to solve the problem below? Given the read cycle diagram below, how long does memory

Can someone please show me the steps and explain how to solve the problem below?

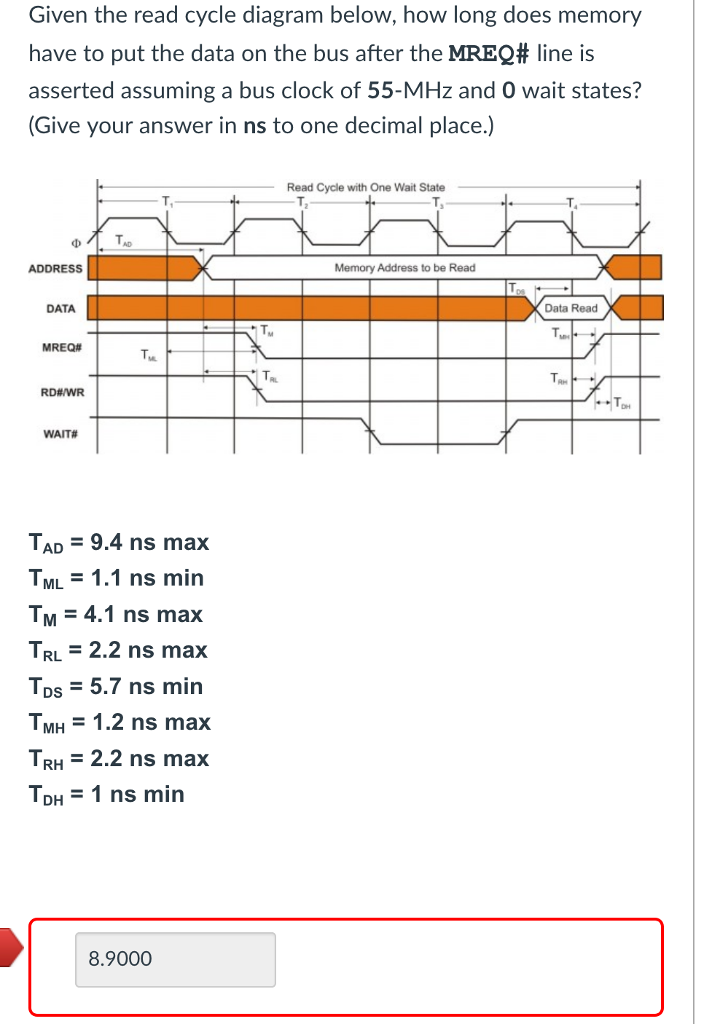

Given the read cycle diagram below, how long does memory have to put the data on the bus after the MREQ# line is asserted assuming a bus clock of 55-MHz and 0 wait states? Give your answer in ns to one decimal place.) Read Cycle with One Wait State ADDRESS Memory Address to be Read DATA Data Read MREQ# RD#WR WAIT# TAD = 9.4 ns max TML= 1.1 ns min IM = 4.1 ns max TRL = 2.2 ns max TDs-5.7 ns min TMH = 1.2 ns max RH.2 ns max TDH-1 ns min 8.9000 Given the read cycle diagram below, how long does memory have to put the data on the bus after the MREQ# line is asserted assuming a bus clock of 55-MHz and 0 wait states? Give your answer in ns to one decimal place.) Read Cycle with One Wait State ADDRESS Memory Address to be Read DATA Data Read MREQ# RD#WR WAIT# TAD = 9.4 ns max TML= 1.1 ns min IM = 4.1 ns max TRL = 2.2 ns max TDs-5.7 ns min TMH = 1.2 ns max RH.2 ns max TDH-1 ns min 8.9000

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts