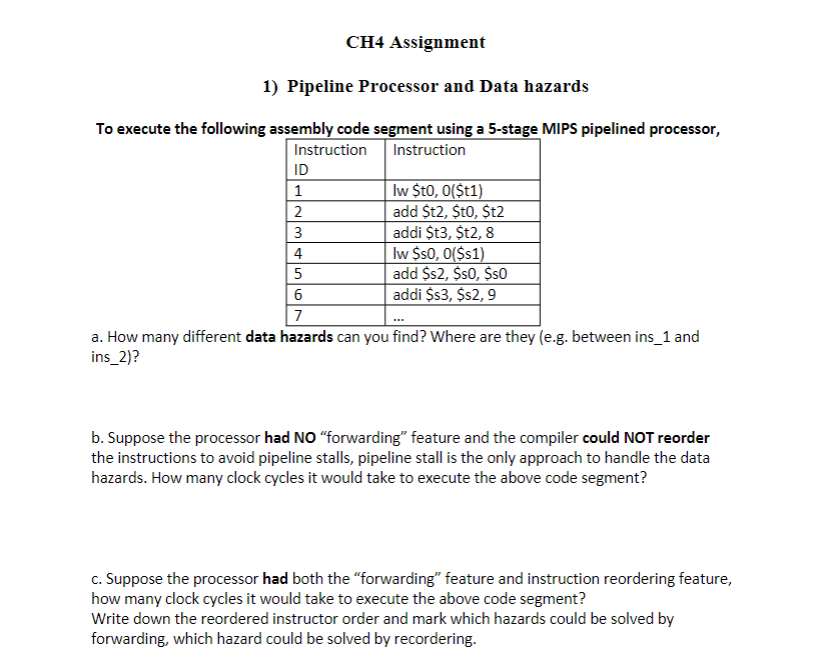

Question: CH 4 Assignment 1 ) Pipeline Processor and Data hazards To execute the following assembly code segment using a 5 - stage MIPS pipelined processor,

CH Assignment

Pipeline Processor and Data hazards

To execute the following assembly code segment using a stage MIPS pipelined processor,

a How many different data hazards can you find? Where are they eg between ins and ins

b Suppose the processor had NO "forwarding" feature and the compiler could NOT reorder the instructions to avoid pipeline stalls, pipeline stall is the only approach to handle the data hazards. How many clock cycles it would take to execute the above code segment?

c Suppose the processor had both the "forwarding" feature and instruction reordering feature, how many clock cycles it would take to execute the above code segment?

Write down the reordered instructor order and mark which hazards could be solved by forwarding, which hazard could be solved by recordering.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock