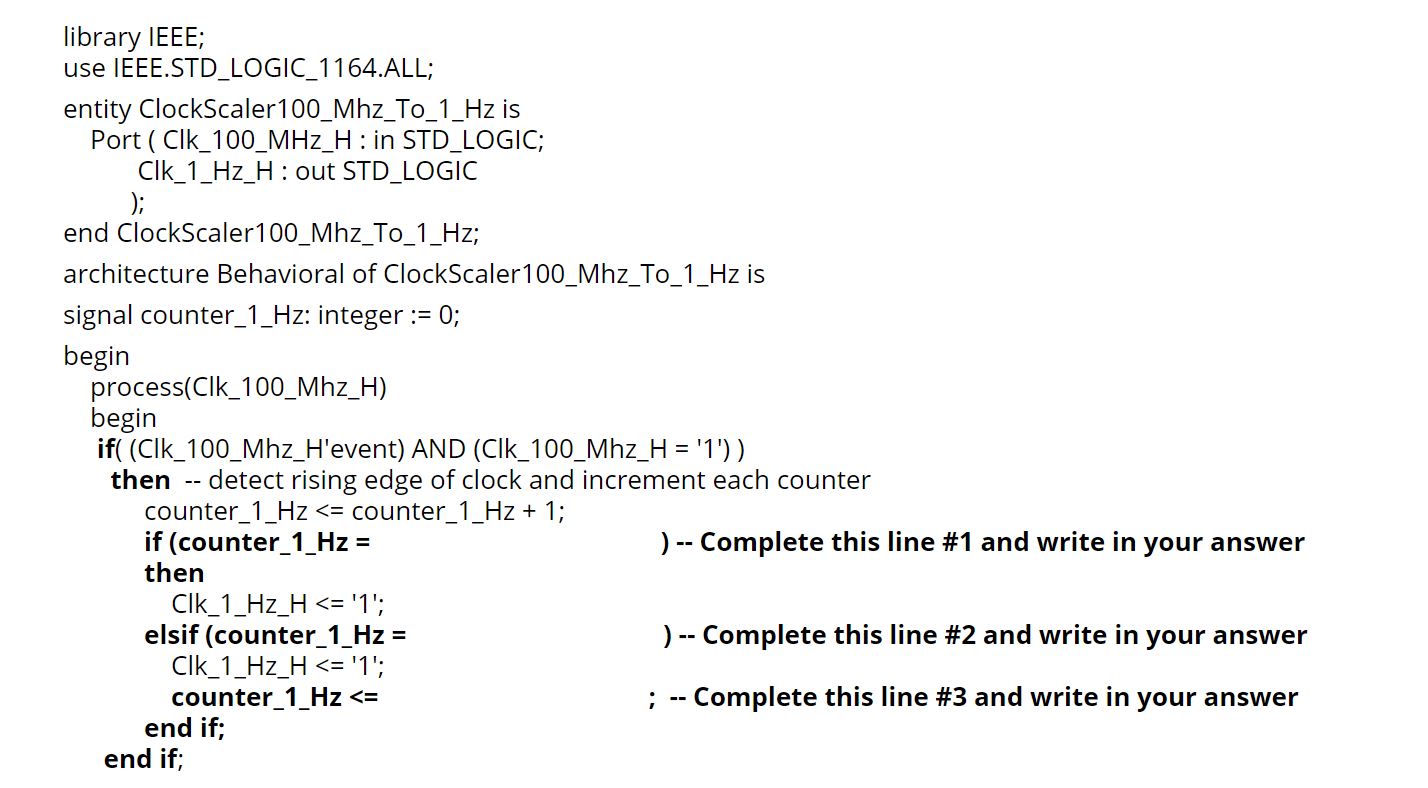

Question: Complete the Scaler model by filling the commented statements library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity ClockScaler 100_Mhz_To_1_Hz is Port ( Clk_100_MHz_H : in STD_LOGIC; Clk_1_Hz_H: out

Complete the Scaler model by filling the commented statements

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity ClockScaler 100_Mhz_To_1_Hz is Port ( Clk_100_MHz_H : in STD_LOGIC; Clk_1_Hz_H: out STD_LOGIC ); end ClockScaler100_Mhz_To_1_Hz; architecture Behavioral of ClockScaler 100_Mhz_To_1_Hz is signal counter_1_Hz: integer := 0; begin process(Clk_100_Mhz_H) begin if( (Clk_100_Mhz_H'event) AND (Clk_100_Mhz_H = '1')) then detect rising edge of clock and increment each counter counter_1_Hz

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts