Question: Computer Architecture (b) Table Q3(b) below shows the instruction mix for a 2 million instruction code for an application running on a fictitious processor at

Computer Architecture

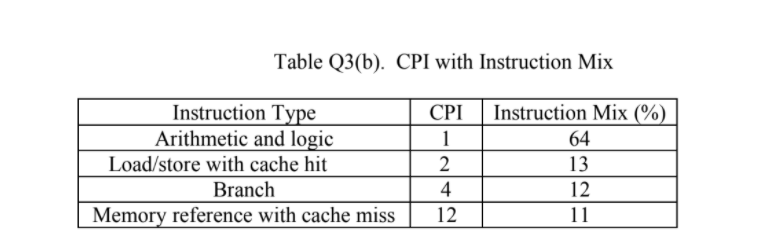

(b) Table Q3(b) below shows the instruction mix for a 2 million instruction code for an application running on a fictitious processor at a clock frequency of 400 MHz. (i) Determine the average CPI and the corresponding MIPS rate. (4) (ii) (8) Now assume that the program can be executed in sixteen parallel tasks or threads with roughly equal number of instructions executed in each task. Execution is on a 16-core system with each core (processor) having the same performance as the single processor originally used. Coordination and synchronization between the parts adds an extra 35,000 instruction executions to each task. Determine the speedup factor by using the 16-core processor. Table Q3(b). CPI with Instruction Mix Instruction Type Arithmetic and logic Load/store with cache hit Branch Memory reference with cache miss CPI 1 2 4 12 Instruction Mix (%) 64 13 12 11

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts