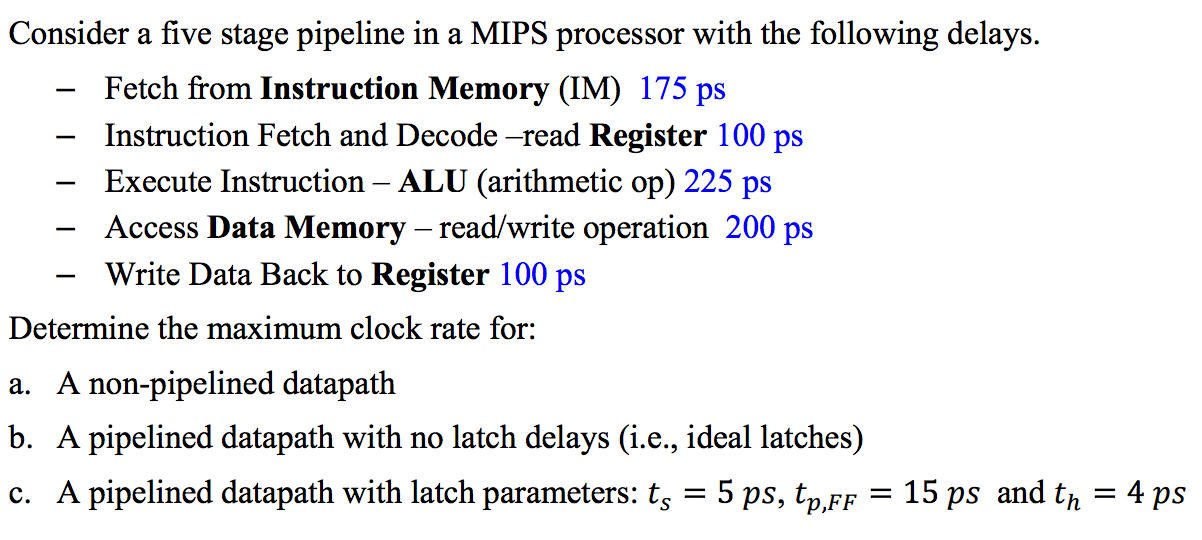

Question: Consider a five stage pipeline in a MIPS processor with the following delays. Fetch from Instruction Memory (IM) Instruction Fetch and Decode -read Register Execute

Consider a five stage pipeline in a MIPS processor with the following delays. Fetch from Instruction Memory (IM) Instruction Fetch and Decode -read Register Execute Instruction - ALU (arithmetic op) Access Data Memory - read/write operation Write Data Back to Register Determine the maximum clock rate for: A non-pipelined datapath A pipelined datapath with no latch delays (i.e., ideal latches) A pipelined datapath with latch parameters: t_s = 5 ps, t_P,FF = 15 ps and t_h = 4 ps Consider a five stage pipeline in a MIPS processor with the following delays. Fetch from Instruction Memory (IM) Instruction Fetch and Decode -read Register Execute Instruction - ALU (arithmetic op) Access Data Memory - read/write operation Write Data Back to Register Determine the maximum clock rate for: A non-pipelined datapath A pipelined datapath with no latch delays (i.e., ideal latches) A pipelined datapath with latch parameters: t_s = 5 ps, t_P,FF = 15 ps and t_h = 4 ps

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts