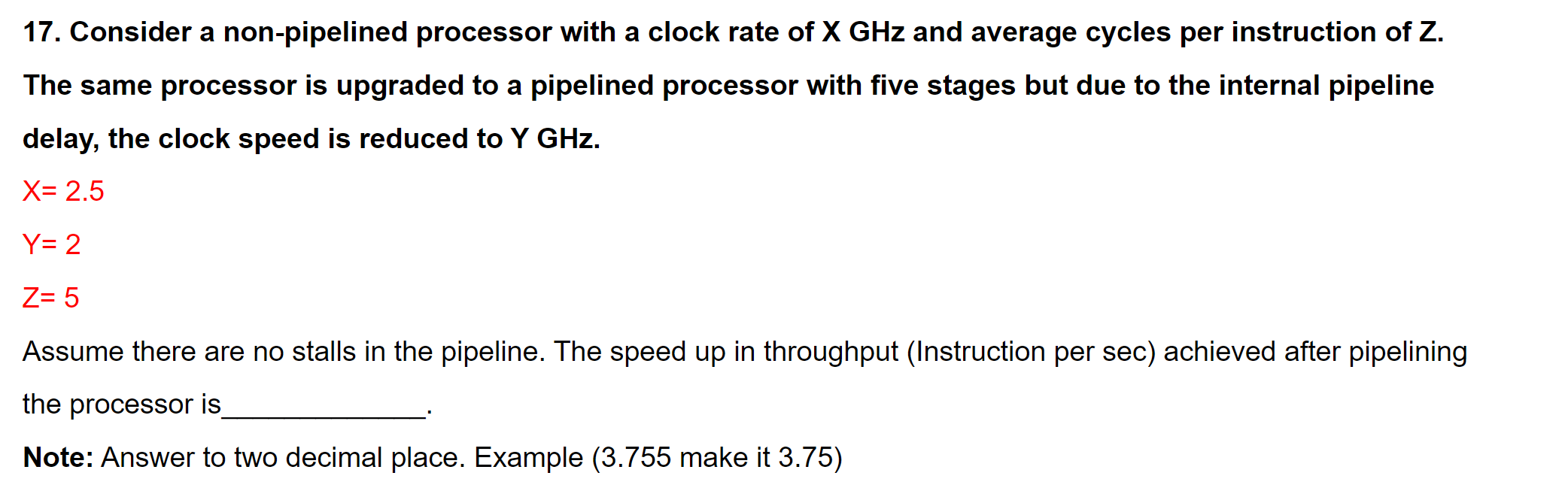

Question: Consider a non - pipelined processor with a clock rate of x G H z and average cycles per instruction of Z . The same

Consider a nonpipelined processor with a clock rate of and average cycles per instruction of

The same processor is upgraded to a pipelined processor with five stages but due to the internal pipeline

delay, the clock speed is reduced to

Assume there are no stalls in the pipeline. The speed up in throughput Instruction per sec achieved after pipelining

the processor is

Note: Answer to two decimal place. Example make it

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock