Question: Consider a single-issue design with a single execution pipeline with five-stages (Fetch, Decode, Execute, Memory, Write Back) capable of beginning execution of one instruction per

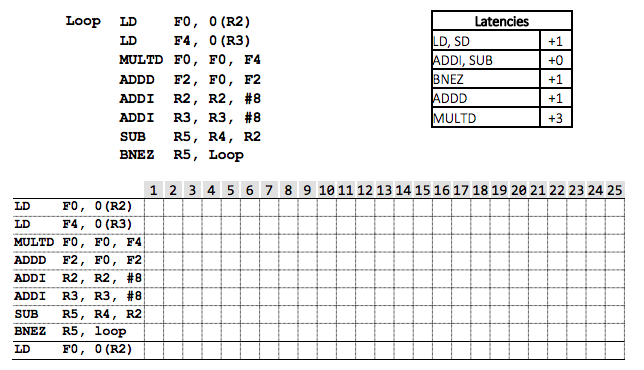

Consider a single-issue design with a single execution pipeline with five-stages (Fetch, Decode, Execute, Memory, Write Back) capable of beginning execution of one instruction per cycle with data forwarding and bypassing hardware, all memory accesses take 1 (one) clock cycle, and all memory references hit in the cache. Assume that the branch is handled by predicting it not taken. Use the following code fragment and assume that the initial value of R4 is R2+440. Please show the timing of the instruction sequence for this pipeline using the given pipeline chart. How many cycles does this loop take to execute?

Loop LDFo, 0 (R2) Latencies LDF4, 0 (R3) MULTD FO, FO, F4 ADDD F2, FO, F2 ADDI R2, R2, #8 ADDI R3, R3, #8 SUBR5, R4, R2 BNEZ R5, Loop LD, SD DDI, SUB BNEZ ULTD 1 2 345 678 9 1011 12 13 1415 16171819 20 21 22 23 24 25 LD FO, 0 (R2) LDF4, 0 (R3) MULTD FO, FO, F4 ADDD F2, FO, F2 ADDI R2, R2, #8 ADDI R3 , R3 , #81 SUB R5, R4, R2 BNEZ R5, loop LD FO, 0 (R2) Loop LDFo, 0 (R2) Latencies LDF4, 0 (R3) MULTD FO, FO, F4 ADDD F2, FO, F2 ADDI R2, R2, #8 ADDI R3, R3, #8 SUBR5, R4, R2 BNEZ R5, Loop LD, SD DDI, SUB BNEZ ULTD 1 2 345 678 9 1011 12 13 1415 16171819 20 21 22 23 24 25 LD FO, 0 (R2) LDF4, 0 (R3) MULTD FO, FO, F4 ADDD F2, FO, F2 ADDI R2, R2, #8 ADDI R3 , R3 , #81 SUB R5, R4, R2 BNEZ R5, loop LD FO, 0 (R2)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts