Question: Consider an initially empty 16-word cache and the following memory access trace of word addresses (whereas CPU addresses are actually 32-bit byte addresses): 2, 3,

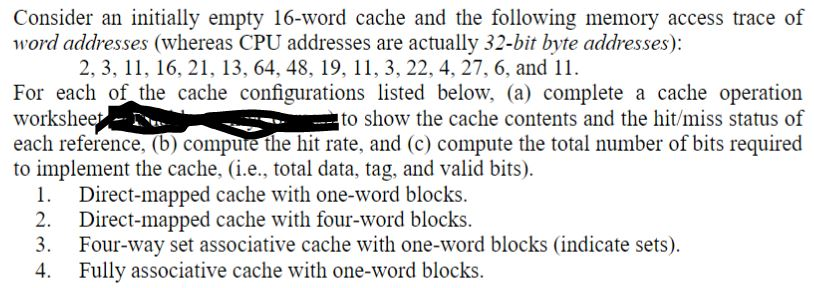

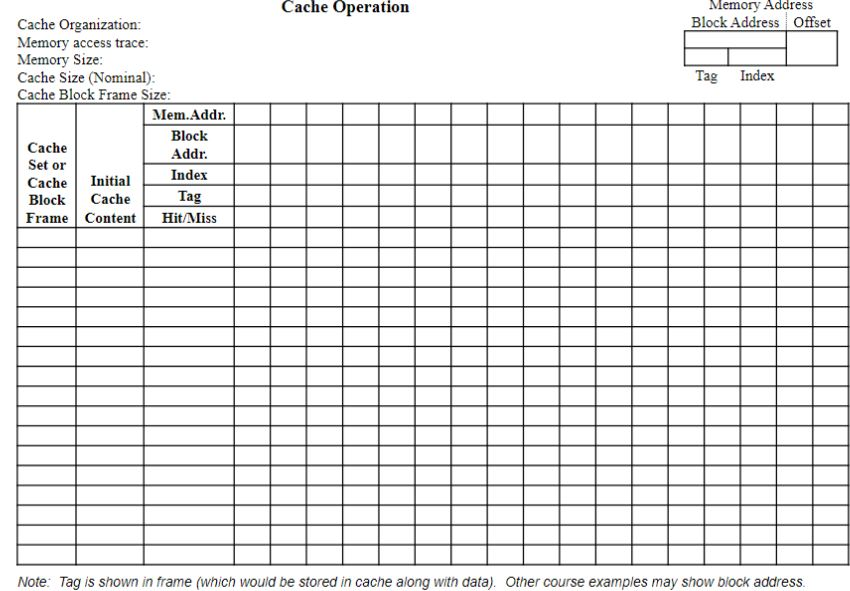

Consider an initially empty 16-word cache and the following memory access trace of word addresses (whereas CPU addresses are actually 32-bit byte addresses): 2, 3, 11, 16, 21, 13, 64, 48, 19, 11, 3, 22, 4, 27, 6, and 11 For each of the cache configurations listed below, (a) complete a cache operation workshe each reference, (b) compure the hit rate, and (c) compute the total number of bits required to implement the cache. (i.e., total data, tag, and valid bits) to show the cache contents and the hit/miss status of 1. Direct-mapped cache with one-word blocks. 2. Direct-mapped cache with four-word blocks. 3. Four-way set associative cache with one-word blocks (indicate sets). 4. Fully associative cache with one-word blocks. Consider an initially empty 16-word cache and the following memory access trace of word addresses (whereas CPU addresses are actually 32-bit byte addresses): 2, 3, 11, 16, 21, 13, 64, 48, 19, 11, 3, 22, 4, 27, 6, and 11 For each of the cache configurations listed below, (a) complete a cache operation workshe each reference, (b) compure the hit rate, and (c) compute the total number of bits required to implement the cache. (i.e., total data, tag, and valid bits) to show the cache contents and the hit/miss status of 1. Direct-mapped cache with one-word blocks. 2. Direct-mapped cache with four-word blocks. 3. Four-way set associative cache with one-word blocks (indicate sets). 4. Fully associative cache with one-word blocks

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts