Question: Consider the below schematic then double check the following code for errors then show your run test. - Using Verilogs UDP coding style, below is

Consider the below schematic then double check the following code for errors then show your run test.

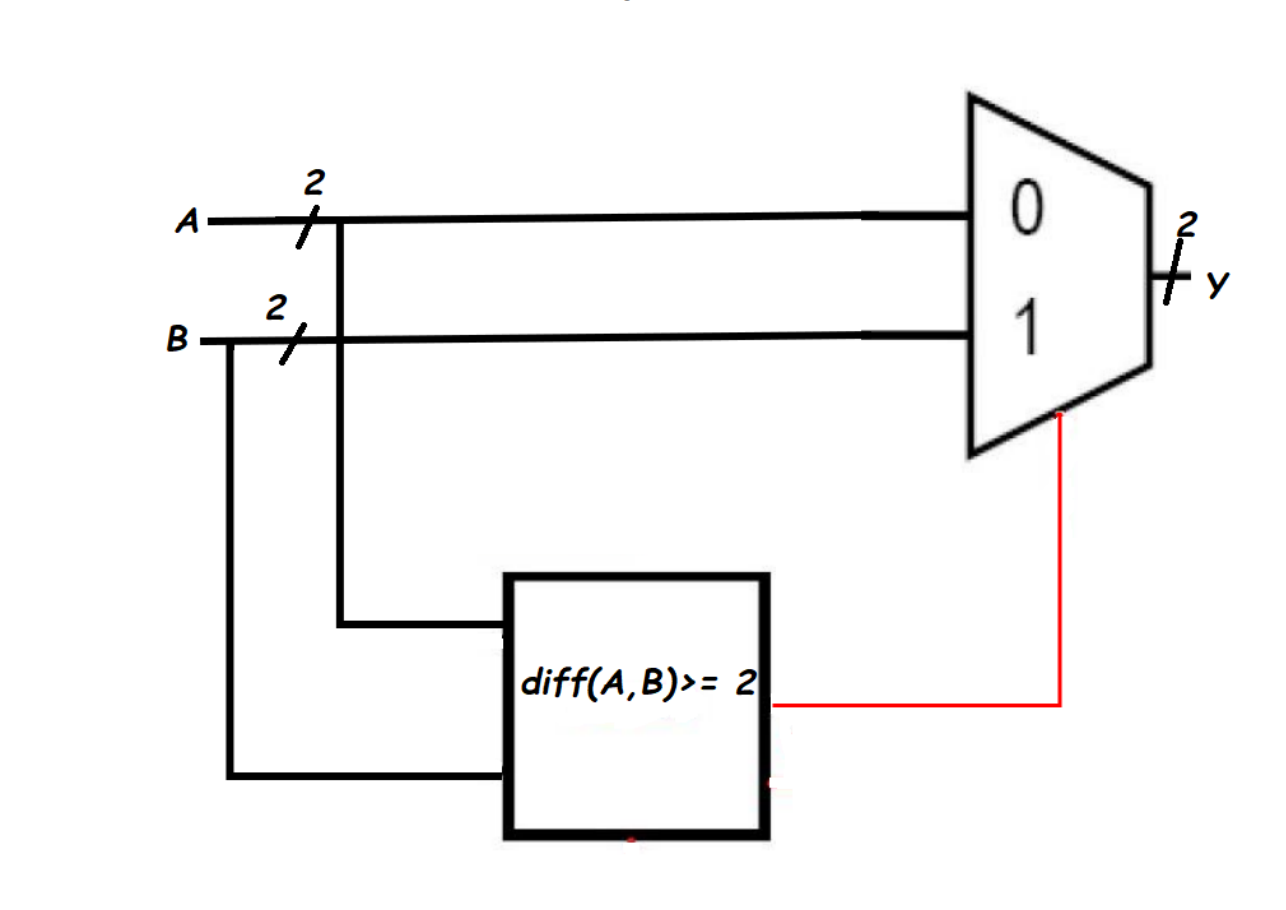

- Using Verilogs UDP coding style, below is the code for diff (A, B) >= 2 knowing that A and B are binary numbers two bits each, thats it, = 10, = 10, the circuit has one output which is 1 when A and B are differ by 2 or more.

module diff_2bits (

input [1:0] A,

input [1:0] B,

output reg out

);

primitive diff2bin;

input [1:0] A,B;

output diff;

table

00: diff = 1'b0;

01: diff = 1'b1;

10: diff = 1'b1;

11: diff = 1'b0;

endtable

endprimitive

diff2bin dbin (

.A(A),

.B(B),

.diff(out)

);

endmodule

-Using Verilogs UDP coding style, below is the code for 2 to 1 MUX

module mux_2to1 (

input sel,

input [1:0] in0,

input [1:0] in1,

output reg [1:0] out

);

primitive mux2to1;

input sel;

input [1:0] in0, in1;

output [1:0] out;

table

0: out = in0;

1: out = in1;

endtable

endprimitive

mux2to1 mux (

.sel(sel),

.in0(in0),

.in1(in1),

.out(out)

);

Endmodule

- this is the test bench for the entire module (MUX and diff)

module mux_diff_tb();

reg [1:0] A;

reg [1:0] B;

reg sel;

reg [1:0] in0;

reg [1:0] in1;

wire [1:0] out;

wire diff_out;

diff_2bits diff (

.A(A),

.B(B),

.out(diff_out)

);

mux_2to1 mux (

.sel(sel),

.in0(in0),

.in1(in1),

.out(out)

);

initial begin

$monitor("A=%b, B=%b, sel=%b, diff(A,B) >= 2: %b, mux(sel=%b, in0=%b, in1=%b): %b", A, B, sel, diff_out, sel, in0, in1, out);

#0 A = 2'b00; B = 2'b01; sel = 1'b0; in0 = 2'b00; in1 = 2'b11;

#10 A = 2'b00; B = 2'b01; sel = 1'b1; in0 = 2'b10; in1 = 2'b01;

#10 A = 2'b10; B = 2'b11; sel = 1'b0; in0 = 2'b00; in1 = 2'b11;

#10 A = 2'b10; B = 2'b11; sel = 1'b1; in0 = 2'b10; in1 = 2'b01;

#10 A = 2'b01; B = 2'b11; sel = 1'b0; in0 = 2'b00; in1 = 2'b11;

#10 $stop;

end

endmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts