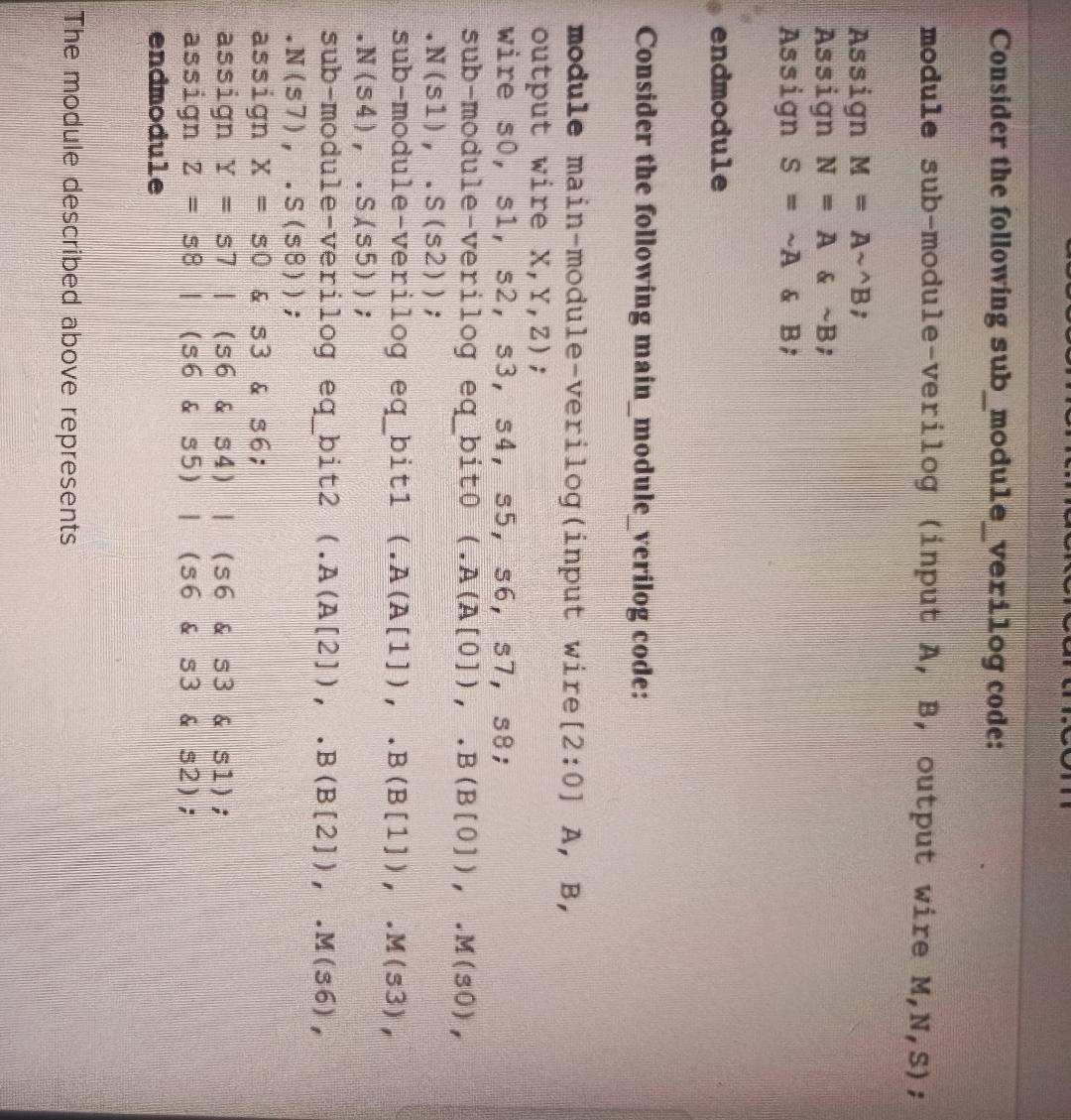

Question: Consider the following sub _ module _ ver 1 1 0 g code: module sub - module - verilog ( input A , B ,

Consider the following submodulever code:

module submoduleverilog input output wire

Assign

Assign &;

Assign B;

endmodule

Consider the following mainmoduleverilog code:

module mainmoulevrilog input wiret: A B output wire ;

wire ;

submoduleverilog eqbito

Consider the following submodulevexilog code:

module submoduleverilog input output wire ;

Assign

Assign &

Assign &;

endmodule

Consider the following mainmoduleverilog code:

module mainmoduleverilog input wire :

output wire ;

wire ;

submoduleverilog eq bito

;

submoduleverilog eqbit

;

submoduleverilog eqbit

;

assign &&;

assign &&&;

assignz&&&;

endimodule

The module described above represents;

submoduleverilog eqbit;

submoduleverilog eqbit;

assign & $ & ;

assign &&&;

endmodule

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock